Other Parts Discussed in Thread: , LMH6553

Hello,

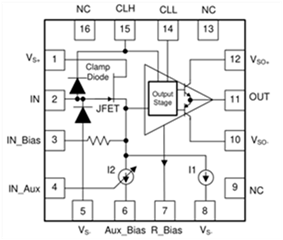

The BUF802 is an interesting device to use on an oscilloscope input and has what appears to be a useful clamping feature to limit the swing into the following signal chain.

The input to the scope (when not using 50R termination) is typically a capacitive divider. e.g. a 10:1 probe could be 9M//10pF and the scope+compensation 1M//90pF. Often you need to look at the small part of a large waveform and this is where the clamping on the BUF802 would help. The input to the probe could be +/-50V which would be +/-5V at the scope input and then you could set the clamp levels to e.g. +/-1V to match the following signal chain.

This works for the negative signal swing because the negative clamp diode is connected to VS-. Hence the scope input can swing down to -5V without any conduction on the clamps.

Setting CLL to -1V will not have any effect on the input signal.

However the positive clamp diode is connected to CLH (not VS+). So setting CLH to +1V will also clip the input signal to +1V + diode drop so about 1.7V. Doing this will cause distortion and offset due to charging of the input divider capacitors.

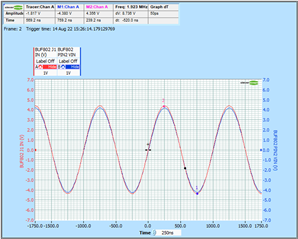

For example, testing with the BUF802RGTEVM using the composite configuration and removing L1 so input is high impedance. Then add a 3:1 capacitive divider (top 27pF//1M, bottom 81pF//333k) and drive with a 26Vpp 1MHz signal so the BUF802RGTEVM J1 input is +/-4.3V.

With CLH = VCC = 5V, CLL = VEE = -5V so there is no clipping I see Pin 2 VIN on the BUF802 (blue trace) closely matches the input signal on J1 (red trace).

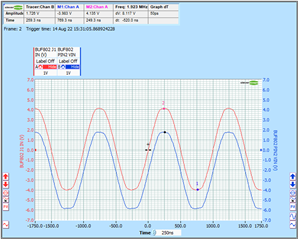

Then reduce CLH from +5V to +1V. The input pin 2 on the BUF802 (blue trace) has been offset by approx 2V and both waveforms have become distorted. This is due to conduction in the positive clamp diode.

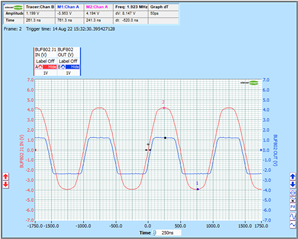

The offset has caused a pulse width error on the BUF802 output (blue trace):

So my question is why was the positive clamps diode connected to CLH and not VS+? It will cause input signal clipping, offset and distortion.

And if there is any plan to have a part where the positive clamp diode is connected to VS+

Thanks, Ken