Other Parts Discussed in Thread: OPA855, OPA858

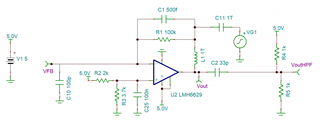

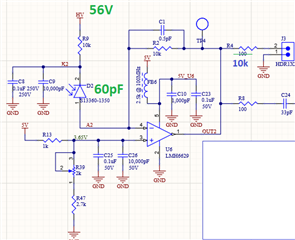

I’m trying to use LMH6629 for single-photon detection from a Hamamtsu S13360 MPPC.

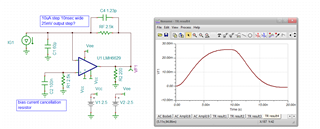

The pulses of current from the MPPC are small and fast. I believe they’re in the 10µA range and last 10ns, depending on the impedance of the input.

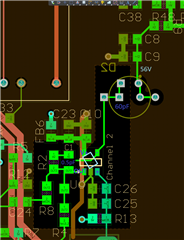

I had problems with the amplifier oscillating in the 700 MHz range. Increasing the feedback capacitor (C1) made the oscillation worse. I removed the ground under the part and around the MPPC anode trace (A2). This helped, but I have had to place a 1000pF decoupling cap on top of the LMH6629 to reduce ringing.

It’s working well now, but here are goals I still have for it:

- Increase stability – Is there a way to inject a signal to measure phase margin? I want to know it won't oscillate if the MPPC's capacitance is a little higher.

- Higher high-frequency gain

In my application I only care about counting the number of photons. I do not need to know the time they arrive.