Hello,

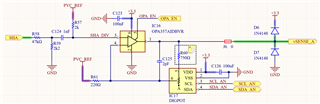

In order to develop a way to treat a input signal to be sampled by a 12 bit ADC, the following circuits were designed:

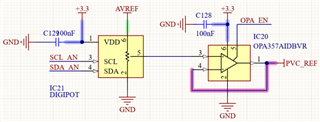

For the reference voltage, we will use this configuration:

Description of the situation:

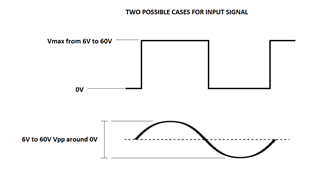

1. Input ignal: The system need to be able to capture two types of signal (from a BLDC or PMSM motor phase), and for each type the signal can vary its amplitude as shown:

* Sinusoidal: Max Vpp = 60V with zero offset and min Vpp = 6V with zero offset;

* PWM of max frequency 200kHz: Max amplitude = 60V and min amplitude = 6V, all with min level ideally at 0v.

2. ADC: 12bit with sampling rate of 0.5uS (Max desirable).

Questions:

1. The circuit was designed to allow the system to vary the offset accordly to each situation. this offsed is applied through the digipot from the 2nd figure. In this configration, is the OPA357 suitable to this application, as the offset could be amplified and thus clamp at the upper limit?

2. If so, by varing the 2nd figure digipot wiper the system should only virtually apply an offset to the signal. Is this correct?

3. For a bandpass configuration, should C125 be removed and then place a capacitor in parallel with D7?

4. Will the R58, R59, C124 and R57 cause a phase delay or a signal distortion?

I would like to ask you to answer these questions to know if this PN is suitable for our application.

We are totally open to suggestions and corrections (please consider suggesting improvements to this system)

Thanks for your attention!