Hello,

I've noticed an issue where occasionally the INA229 starts sending invalid / unexpected data on MISO back to the STM32 main micro. This usually happens when the micro (not INA229) is soft reset or power cycled. After this occurs the INA229 keeps sending invalid data until it is power cycled. Sending a reset command via CONFIG register does not fix the issue.

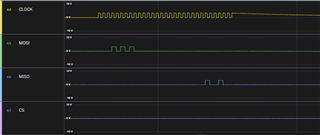

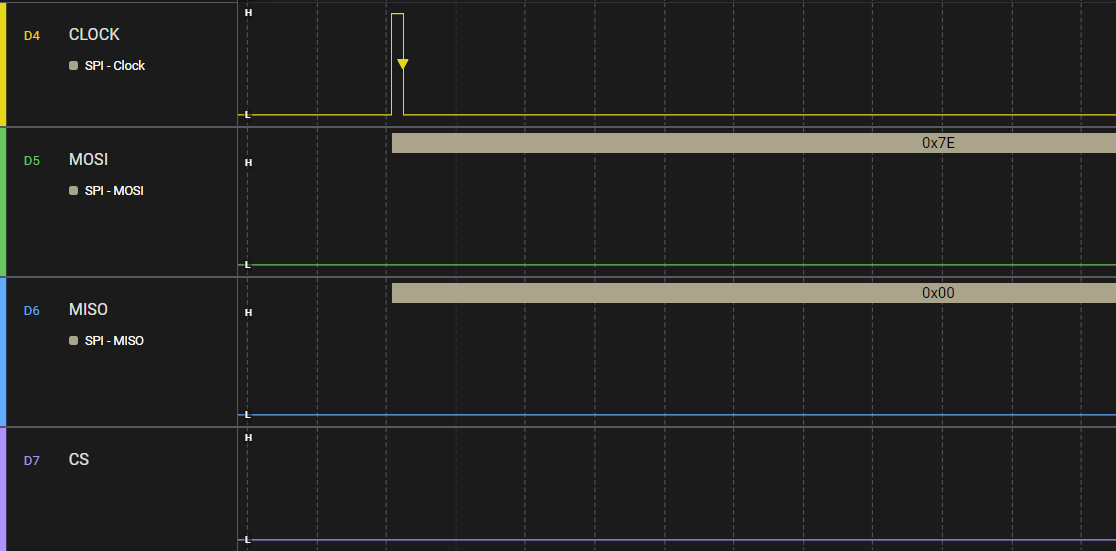

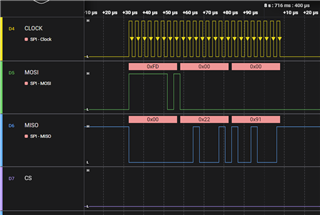

Valid Data Example: Requesting Device ID by sending 0xFD, correctly receives 0x2291

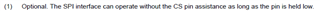

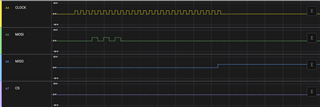

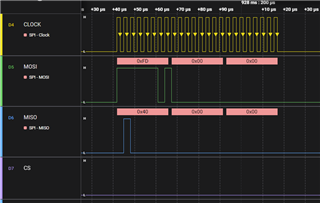

Invalid Data Example: Requesting Device ID by sending 0xFD, Receiving 0x40 before the command is even sent out.

Once the INA229 gets in this state I cannot get it to send rational data back until a full power cycle. Sending reset command does not work. In both examples CS is pulled low at all times (only one device on the bus).

Any help to understand what causes this issue and how to fix it would be appreciated.

Thank you!