Hello team ,

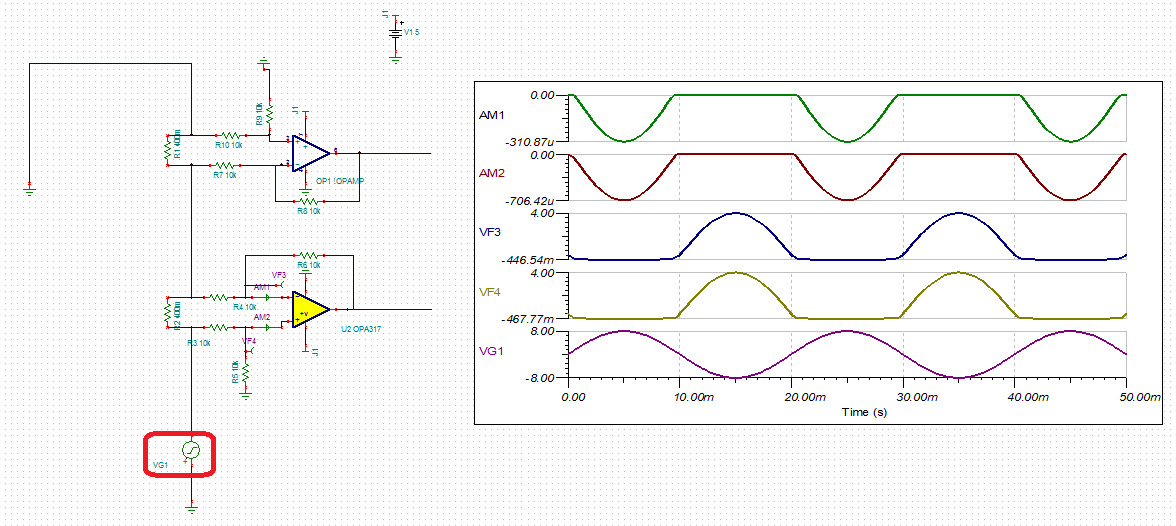

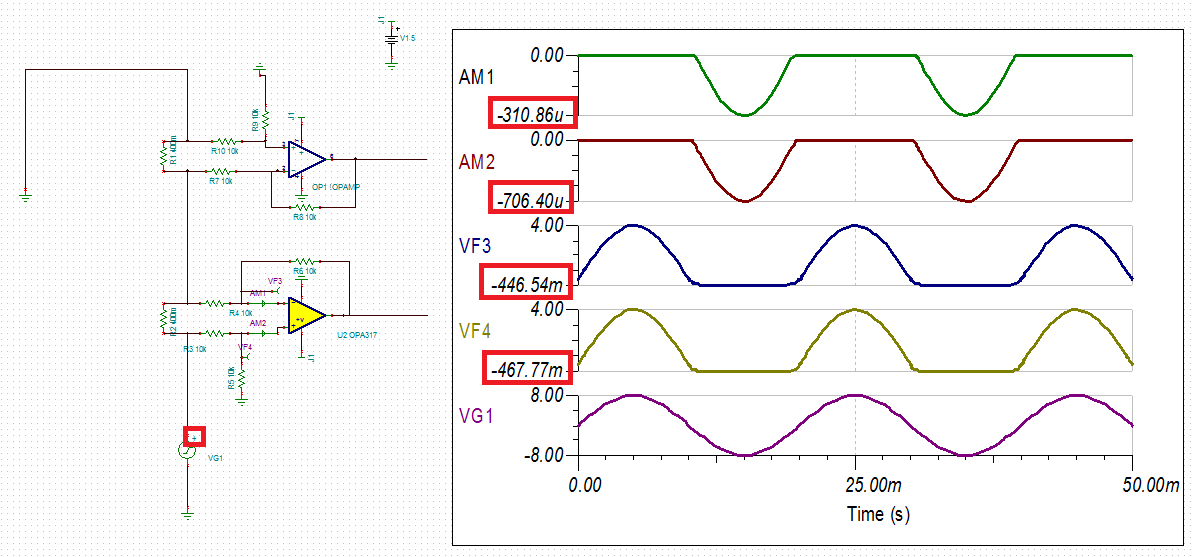

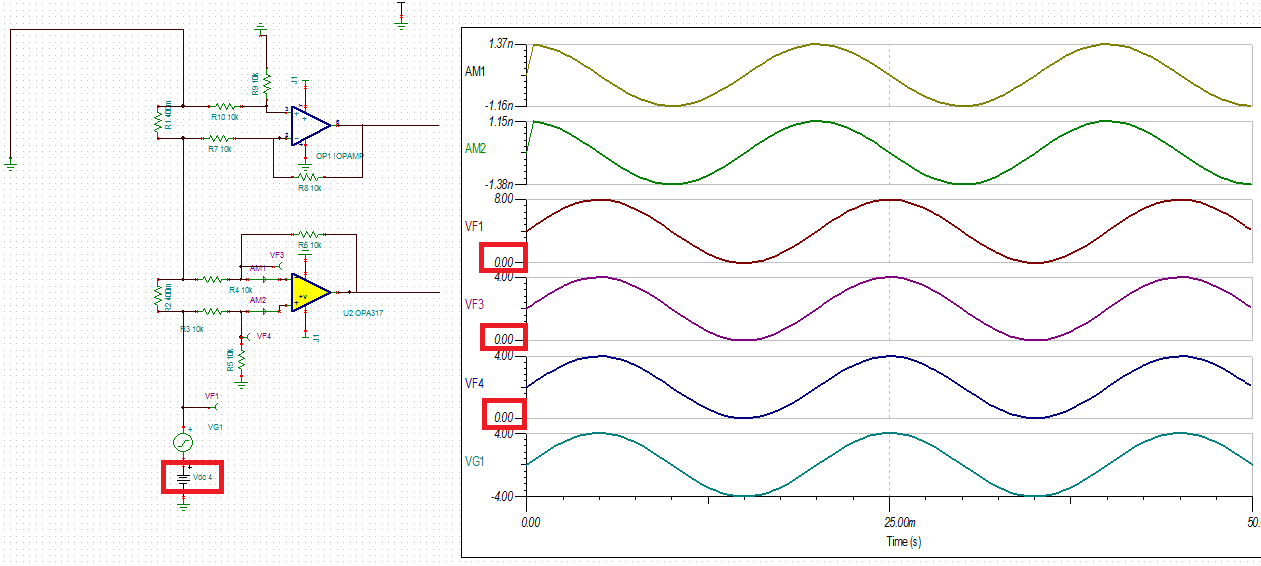

some of my customers are using the circuit attached below as a bi directional current sense

Inverter_current_monitor.TSCBasically each op amp gives voltage across the rsense in half cycle

outputs of these op amps go to the uC where they are read

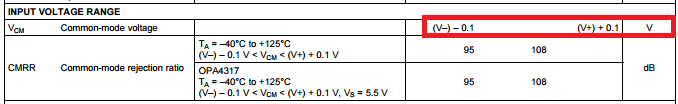

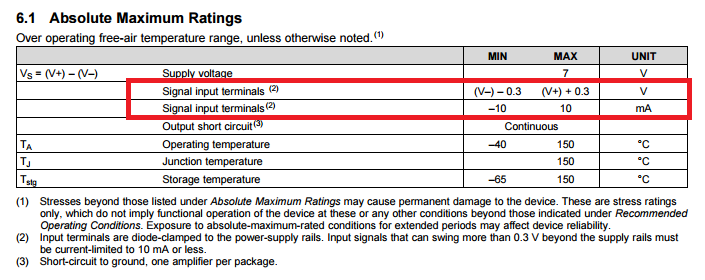

in my conversation with BU , it was pointed out that this architecture would violate the Absolute maximum ratings of the input pins of the op amp

However due to the high value resistance connected at the input the current flowing through the internal diodes is limited

Can you please help me understand more about this architecture , and if we are indeed violating the input absolute max specs can we modify it slightly to make it acceptable

Thank you