How is this time generated and how is it cancelled?

The chart below shows the frequency variation from 50-100Mhz and a 20us delay.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

hello Fung,

The triger signal is writing R0 register .

Current status:

fosc = 10Mhz ,fpd =50Mhz

there is no 20us delay at 1.3Ghz-2Ghz or greater than 3.75Ghz.But the calibration time becomes longer, greater than 200 us.

this time use the calibration mode is Close Frequency Assist.

I use the Partial assist mode and full assist mode in the past.

The programming sequence for changing frequency is :(for example change to 100Mhz)

1. Calculate the frequency division value according to the output frequency, the R45 register [12:11] OUTA_MUX select 0 Channel divider ,

R45 register :0x2DC0DF;

the R75 register CHDIV= 11;

R75 register : 0x4B0800&(11<<6)

2.VCO frequency : Fvco=fout *CHDIV=100000*11=1,100,000 (fout :out frequency 100mhz )

3.Calculate the n-division value:Freq_N=Fvco/50000.000000;(fpd =50mhz)

4.Integer frequency division :PLL_N=(unsigned long)Freq_N;

R36 register : PLL_N|0x240000

5.Fractional frequency division :PLL_NUM=(FreqVCO-PLL_N*50000)*PLL_DEN/50000.0000;

PLL_NUM_MSB=PLL_NUM/65536;

PLL_NUM_LSB=PLL_NUM%65536;

R43 register : PLL_NUM_LSB&0x2B0000

R42 register : PLL_NUM_MSB&0x2A0000

6.R0 register :0x00241C

Hi Nze,

When you switch to 100MHz, did you program the following registers in sequence?

1. R45 to set OUTA_MUX to "channel divider"

2. R75 to set the CHDIV value (ps: div/11 is not a valid value, only even numbers are supported)

3. R36 to set the PLL_N value

4. R43 and R42 to set the PLL_NUM value

5. R0 to trigger VCO calibration

The programming sequence is fine. If you have OUT_FORCE = 0 and OUT_MUTE = 1, when you use the CS# signal of R0 to trigger the test equipment, there will be no output for some time while the VCO is being calibrated. Since you are using close frequency assist, depending on the existing and new VCO frequency, the calibration time could vary a lot. If both frequencies are very close and within the same VCO core, the calibration time will be very short.

However, if you were switching the output frequency from 50MHz to 100MHz, all you need to program is CHDIV. A VCO calibration is not required.

Hello Fung,

I haven't received your reply for a long time. I'm a little worried about you.

I program the register order you sent me.

I use the close frequency assist recently,and I test it that OUT_FORCE = 1 and OUT_MUTE =0, or OUT_FORCE = 0 and OUT_MUTE =0.The No frequency output time is still 20ms. It's so strange.

Hi Nze,

Is the problem happen when the VCO frequency falls into below zone?

I can't remember the behavior of close frequency assist, but with auto-calibration, if you have OUT_FORCE = 0 and OUT_MUTE = 1, the output will not mute during calibration.

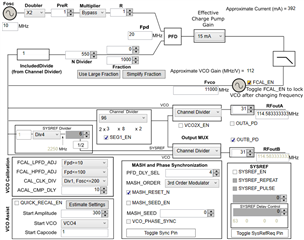

Let's try an experiment, run the following configuration to make the VCO lock to 11000MHz with auto-calibration. Then program PLL_N to 551 and then program R0 to trigger auto-vco calibration.

Next, repeat the above experiment but make QUICK_RECAL_EN = 1 before programming PLL_N to 551. Will the output be muted?

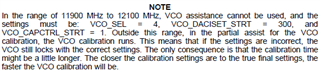

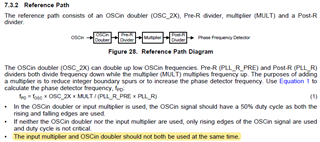

BTW, there are min. input frequency and max. output frequency requirement to the MULT, we cannot get 50MHz fpd from a 10MHz reference.

Hi Fung,

1. I've tested it in the range of 11900 MHz to 12100 MHz,The output be muted, time is still 20ms.

2.Sorry,Are you writing wrong? The mute output should be OUT_FORCE = 0 and OUT_MUTE = 1;

3. I've tested an experiment,The output be muted, time is still 20ms.

I use TISC Pro to generate hex files as follows:

R112 0x700000 R111 0x6F0000 R110 0x6E0000 R109 0x6D0000 R108 0x6C0000 R107 0x6B0000 R106 0x6A0000 R105 0x690021 R104 0x680000 R103 0x670000 R102 0x660000 R101 0x650011 R100 0x640000 R99 0x630000 R98 0x620000 R97 0x610888 R96 0x600000 R95 0x5F0000 R94 0x5E0000 R93 0x5D0000 R92 0x5C0000 R91 0x5B0000 R90 0x5A0000 R89 0x590000 R88 0x580000 R87 0x570000 R86 0x560000 R85 0x550000 R84 0x540000 R83 0x530000 R82 0x520000 R81 0x510000 R80 0x500000 R79 0x4F0000 R78 0x4E0003 R77 0x4D0000 R76 0x4C000C R75 0x4B0AC0 R74 0x4A0000 R73 0x49003F R72 0x480001 R71 0x470081 R70 0x46C350 R69 0x450000 R68 0x4403E8 R67 0x430000 R66 0x4201F4 R65 0x410000 R64 0x401388 R63 0x3F0000 R62 0x3E0322 R61 0x3D00A8 R60 0x3C0000 R59 0x3B0001 R58 0x3A9001 R57 0x390020 R56 0x380000 R55 0x370000 R54 0x360000 R53 0x350000 R52 0x340820 R51 0x330080 R50 0x320000 R49 0x314180 R48 0x300300 R47 0x2F0300 R46 0x2E07FC R45 0x2DC0DF R44 0x2C1FA3 R43 0x2B0000 R42 0x2A0000 R41 0x290000 R40 0x280000 R39 0x2703E8 R38 0x260000 R37 0x250404 R36 0x240226 R35 0x230004 R34 0x220000 R33 0x211E21 R32 0x200393 R31 0x1F43EC R30 0x1E318C R29 0x1D318C R28 0x1C0488 R27 0x1B0002 R26 0x1A0DB0 R25 0x190C2B R24 0x18071A R23 0x17007C R22 0x160001 R21 0x150401 R20 0x14E048 R19 0x1327B7 R18 0x120064 R17 0x11012C R16 0x100080 R15 0x0F064F R14 0x0E1E70 R13 0x0D4000 R12 0x0C5001 R11 0x0B0018 R10 0x0A10D8 R9 0x091604 R8 0x082000 R7 0x0740B2 R6 0x06C802 R5 0x0500C8 R4 0x040A43 R3 0x030642 R2 0x020500 R1 0x010808 R0 0x00241C

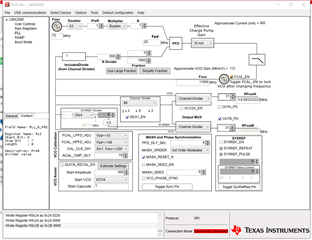

code:

0x4E0003|(1<<9); //R78 QUICK_RECAL_EN :1 PLL_N= 551; 0x220000; //R34 0x240000|PLL_N; //R36 TP_H; //Trigger level High R0; //R0 TP_L; //Trigger level Low

Hi Nze,

I am sorry, it was a typo, the output will not mute when OUT_FORCE = 1 and OUT_MUTE = 0.

Did you mean, you got the output muted with both auto-calibration and quick_recal_en=1 ? if this is true, I will have to ask my colleague to verify this.

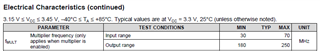

The MULT frequency requirement is specified in the datasheet.

Hi Fung,

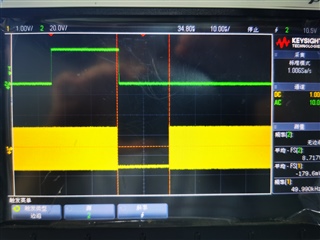

Does the green trace refer to my reply on June 22? That line is the trigger signal for writing the R0 register,Pull up before writing R0 and pull down after writing. such as in my code TP_ H is Pull up, TP_ L is Drop down.

Yellow is the output frequency. In the oscilloscope window, each grid is 10us, and there is no frequency in the middle. The time of two grids is just 20us.

So the mute time is 20µs.