Hi everyone,

I have a question about the relationship between the input clocks of PLL1 and PLL2 for LMK04828.

Why PLL1 input clock is 10MHz but PLL2 input is 100MHz? If change it, it will wrong?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi everyone,

I have a question about the relationship between the input clocks of PLL1 and PLL2 for LMK04828.

Why PLL1 input clock is 10MHz but PLL2 input is 100MHz? If change it, it will wrong?

Hello Nan,

10MHz is a common standard reference signal across many pieces of test and measurement equipment, so it is helpful to provide the ability to lock frequency of the LMK04828 on the board with other equipment such as signal generators, frequency counters, spectrum analyzers, etc.

I don't think the answer above does a good job of explaining why this system-level design decision occurs commonly across many pieces of test and measurement equipment, so I will also try to explain this design decision as well. There are typically two reasons why someone might choose to use a dual-loop jitter cleaner:

Changing the input frequency to the PLL may or may not have an effect. If you changed the reference input from 10MHz to 100MHz, but the phase detector remained the same frequency, nothing would change. On the other hand, if you changed the phase detector frequency to accommodate the higher possible range with a 100MHz reference, this would alter the loop gain and the stability. We have a calculation tool, PLLatinum Sim, which allows you to examine the effect of these changes yourself.

I will also point out our TI Precision Labs training series which goes over the fundamental aspects of PLL design and system implications in great detail.

Regards,

Derek Payne

Hi Derek,

If PLL1 is just for reducing jitter of VCXO, so why not use 100MHz VCXO connect clock input ports directly?

Is it the problem of the phase detector inside the LMK04828 as you said before?

Regard,

Nan

Nan,

You could just use the 100MHz VCXO, but the frequency of the VCXO will be 100MHz + ε, where ε is some small error relative to absolute 100MHz due to temperature drift or control voltage tuning range. If you tried to measure the PLL output frequency with a frequency counter or some other instrument that was specified as "perfect" 100MHz (at least for the purposes of comparison), there would be some difference ε * Fout/100MHz in the measured output frequency due to the error from the VCXO.

Recall that most instruments include a 10MHz reference on-board, and this reference can be brought out of the instrument or another instrument's 10MHz can instead be connected to override the on-board 10MHz. This is an industry-standard synchronization mechanism between different instruments which must work with frequency, such as frequency counters, spectrum analyzers, oscilloscopes, etc.

By including PLL1, we can take the built-in 10MHz reference oscillator output on the frequency counter or other instrument and provide it as a reference into LMK04828 PLL1, which eliminates the measurement error. Alternately, we can buffer a copy of the on-board 10MHz reference, and connect the buffered copy to the 10MHz reference oscillator input on the frequency counter. Then, by locking the VCXO to the 10MHz reference on the PCB, the error from the 10MHz reference would be common for both the PLL and the frequency counter. We could take the 10MHz directly to PLL2 and omit the VCXO and PLL1, but the phase detector frequency would be an order of magnitude lower and the PLL performance would be 10dB worse in-band. We have no way to lock the VCXO to an external reference without PLL1. We could add a buffer/divider to divide-by-10 and transmit the VCXO reference off-board to our instruments, and simultaneously provide 100MHz to PLL2... but this requires a lot of extra devices, and still gives us no way to lock the VCXO to an external instrument's 10MHz reference.

It is worth noting that usually the 10MHz reference has very good close-in noise (maybe up to 1kHz) but sometimes the instrument's 10MHz reference has a very high noise floor compared to a VCXO. So PLL1 still frequently behaves as a jitter cleaner in this scenario, even while locking a VCXO to an external reference and increasing the phase detector frequency at PLL2.

Regards,

Derek Payne

Hi Derek,

Do you have some tutorials or examples about configuring LMK04828, thank you!

Regards,

Nan

Nan,

While we don't have anything comprehensive, we do have default configurations that show final/working register state, and TICS Pro has some features (set modes page, SYNC/SYSREF procedure declarations) which can simplify some aspects of the configuration process.

To your point, a flowchart or a decision tree could improve usability. I'll make a note of this for future datasheets.

Regards,

Derek Payne

Hi Derek,

Thank you very much, I will try to use the TICS Pro.

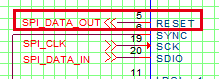

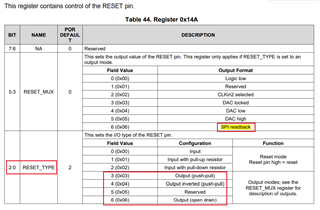

Another question, I want to configure the RESET pin of LMK04828 as the SPI data out pin(Figure 1), but I don't know choose which output mode(Figure 2).

Thanks again,

Nan

Nan,

Output (push-pull) works like a standard CMOS output driver, logic high = 3.3V and logic low = 0V. Output inverted (push-pull) is the same thing, but inverted: logic high = 0V, logic low = 3.3V.

Output (open-drain) assumes an external pull-up resistor is used. Open-drain makes the most sense when the I/O returned to the microcontroller/FPGA/etc. utilizes 2.5V or 1.8V I/O, since the pull-up resistor can be connected to the programmer I/O supply instead of the device internal 3.3V rail for logic high signals. Open-drain is also useful if the readback bus must be shared with another device.

Regards,

Derek Payne

Hi Derek,

1) If I use push-pull, may I debug this signal by ILA Core in FPGA?

2) And "SPI readback ", which means SDO(read data) of the LMK04828?

By the way, I want to use SPI 4-wire mode.

Regards,

Nan

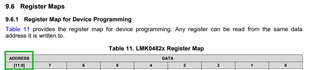

Hi Derek,

I find something,,, uh,,,maybe wrong in LMK0482X datasheet, because it said that the Address bit-width is 13, but somewhere is 12.

Address bit-width is 13, but somewhere is 12

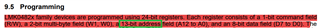

Yes, this is a mistake in the datasheet. There are three registers corresponding to the SPI_LOCK field which set the 13th bit to access. I'll put it on the list of things to fix in the next revision.

1) If I use push-pull, may I debug this signal by ILA Core in FPGA?

Yes, this should be possible. I'm not totally sure how the ILA core is implemented, but it should have the ability to monitor any signals on the I/O once they get latched into the FPGA registers somewhere.

2) And "SPI readback ", which means SDO(read data) of the LMK04828?

Yes, SPI readback output type corresponds to the SDO readback data.

By the way, I want to use SPI 4-wire mode.

As long as one of the GPIO is configured as SPI readback, SPI 4-wire mode will be active. Note that technically it is possible to use 3-wire and 4-wire mode simultaneously; if you want to use 4-wire mode and also disable 3-wire mode, make sure SPI_3WIRE_DIS=1 (this should be the default).

Regards,

Derek Payne

Hi Derek,

I want to know the power level standard of the SPI signal in LMK0482x device, I don't find it in its datasheet.

Regards,

Nan

Hi Nan,

LMK0482x can accept 1.8V, 2.5V, or 3.3V SPI. The SDO readback signal can interface with 1.8V or 2.5V systems in open-drain mode.

Regards,

Derek Payne