Other Parts Discussed in Thread: ADS42JB46EVM, LMK04832, CDCLVP111-SP, LMK03328, ADS42JB46

Hi everyone,

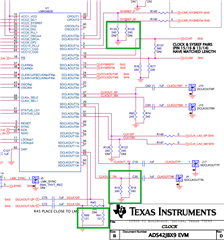

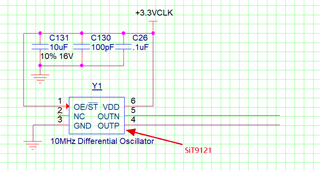

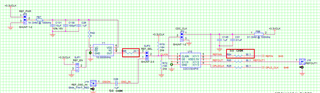

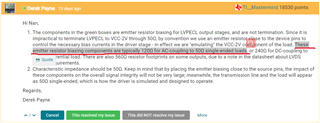

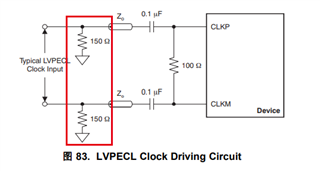

1) I don't know why there are 3 kinds "impedance matching" in the design schematic of LMK04828 (in ADS42JB46EVM) because I think the Clock-output pins are same.

2) How should I choose the resistance size for impedance matching, because I don't know the characteristic impedance of the transmit line.

Thanks for all replies.