Other Parts Discussed in Thread: LMK05318

Hi all

Would you mind if we ask LMK05028?

<Question1>

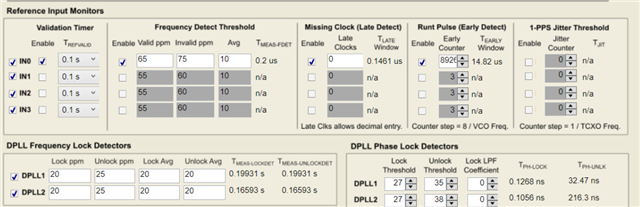

How much of value should we set these value?

-Frequency Detect Threshold

-DPLL Frequency Lock Detectors

-DPLL Phase Lock Detectors

-XO input tolerance : ±25ppm

-Reference input tolerance : ±30ppm

<Question2>

Is it to possible to operate following reset in a row?

Register R12 : Software Reset ALL functions

Register R676 : Software Reset Output Channels

Register R677 : Software Reset PLL2 , Software Reset PLL1

As the background of this question, the customer operates "Register R12 : Software Reset ALL functions" in a row", the output clock was not unstable.

Kind regards,

Hirotaka Matsumoto