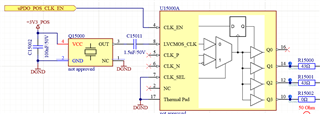

Other Parts Discussed in Thread: LMK00804B

Dear experts,

we got a design were a 38.4MHz TCXO with a 0.95V amplitude is AC decoupled connected to "LVCMOS_CLK".

Buffer is supplied with 3V3.

Its interesting because at buffer output a proper LV-CMOS 38.4MHz signal is available.

I'm a little bit confused why because in datasheet the minimum value for ViH is specified with 2V.

Thanks,

Martin