Hi Texas,

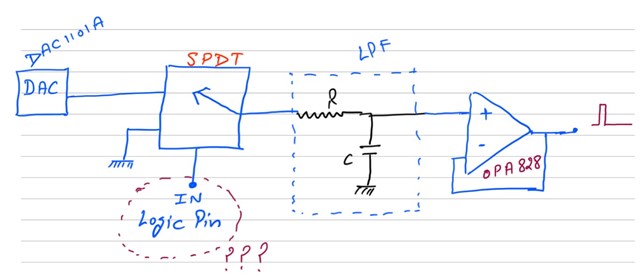

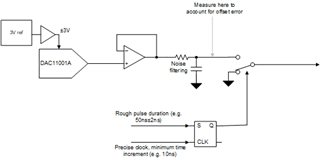

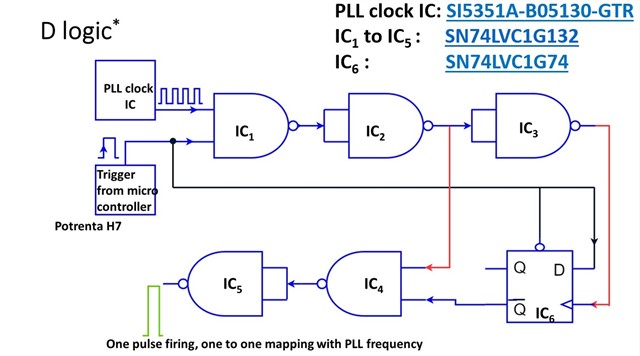

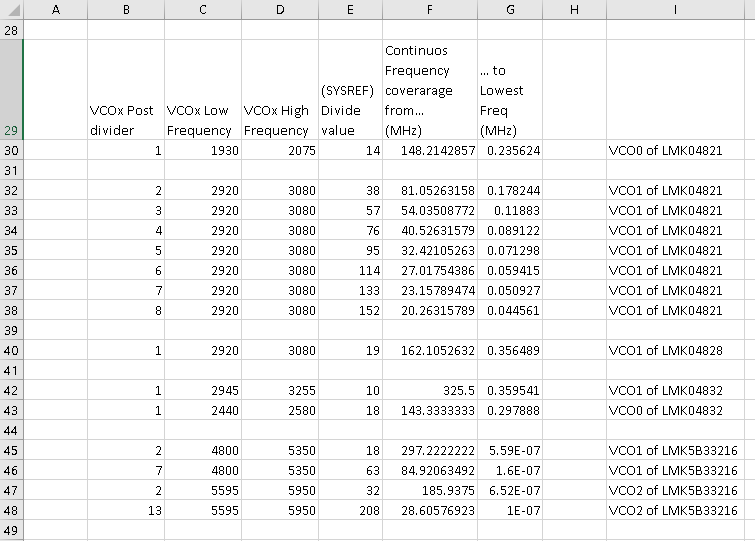

I want to generate an ultra-low noise, low voltage pulse (10 mV peak to peak, 10 nsec pulse duration) at a very high frequency. My requirement is to vary the pulse amplitude from 10 mV pp to 2.5 V pp, also pulse width variation from 10 nsec to 100 msec.

Could you please suggest possible efficient solutions which can be realized using discrete component ICs? This low-voltage, low-amplitude pulses will be given to the memory device array (in-house fabricated) via TMUX1108. Output current (1nA to 1mA) will be further sensed using LMP7721 multiple feedback gains.

Kindly help.

Thanks

Deepak