Hi there,

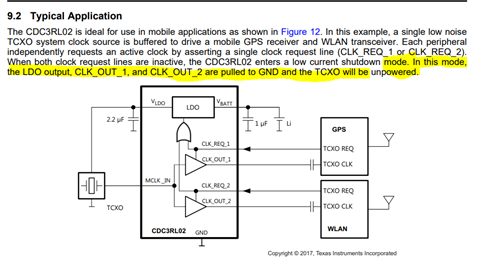

two questions about the CDC3RL02BYFPR

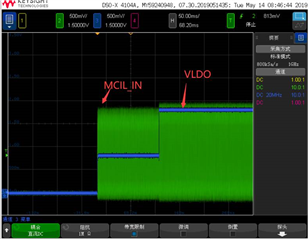

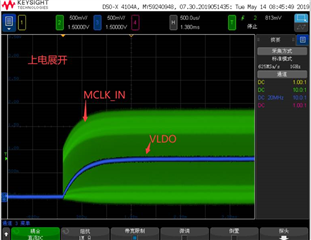

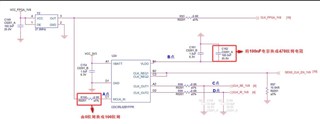

Test condition. the vbatt Is on, MCLK_In is 27Mhz

1. the vldo output is 0.8 when is CLK_REQ is low. The Vldo goes to 0v if MCLK_in is removed.

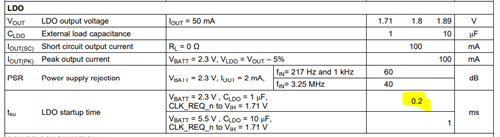

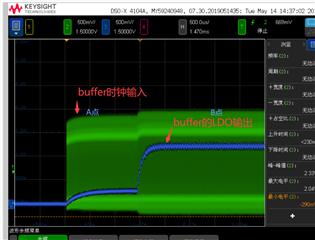

2. the VLDO output clk has 200 us delay after CLK_REQ is on.

are this two behaviors normal operation?

BRs

Shubiao