Other Parts Discussed in Thread: CDCLVP111

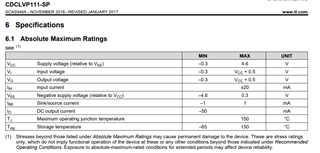

The answers to previous questions about single-ended inputs are inadequate. Is it really true that the max VID for a single leg is 1.3V, such that the part will be damaged by a 3.3V single-ended input connected as shown in Fig. 8? Or is this just a characterization limit, because the part has not been tested with single-ended inputs, and the design would be tolerant to greater swings?

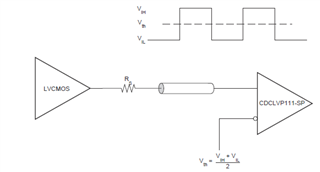

If there really is a risk of damage, the datasheet figure 8 (shown below) is highly misleading. It would only work for a 1.2V LVCMOS output, which is rarely seen in oscillators. But I question whether 1.3V is really the threshold where the part will start to have problems.

Another problem: in the datasheet, VCM min for CLKn is 1V. In another question/answer, it is stated that this must be satisfied for single-ended input. This appears to completely contradict the picture above, if a voltage division is required. To state the obvious, an LVCMOS signal divided down to 1.3V will have a VCM of 0.65V, which is less than 1V. Reconciling this would require the addition of AC coupling + DC biasing. Please explain these inconsistencies.