- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

I have a 10 MHz clock signal and I am attempting to create a frequency-syntonized output with a known phase offset.

I have the 10 MHz input connected to PRIREF with the DPLL enabled and I have the output on OUT0 using APLL1. I am attempting to adjust the phase of the output using the DPLL_REF_SYNC_PH_OFFSET register. I have three questions/issues that I am looking for answers to.

First, without applying any offset through DPLL_REF_SYNC_PH_OFFSET, I would expect that if the output on OUT0 is phase-locked to the input on PRIREF then hitting soft reset on the 5318 would not affect the phase offset between the the input and output. However, each time I hit soft reset and the PLL reacquires a lock, the output settles to a random phase offset from the input. Is this expected behavior, and if so, why? Is this a configuration issue?

Second, can the DPLL_REF_SYNC_PH_OFFSET register be used in the manner I am attempting? In other words, can you use that register to create a known phase offset between the input and output of the 5318?

Third, assuming that the answer to the previous question is yes, is it possible to make such an adjustment in real-time? Experimenting with the eval board, it appears that any change to the DPLL_REF_SYNC_PH_OFFSET register is only read if you perform a soft reset of the chip. It seems like the device should read register changes as they are made, not requiring the chip to be reset. Is this the case?

Thank you all in advance for any help you can provide.

Josh White

I am attaching the .tcs file I used to program the board in case it's of assistance. 10MHz-test.tcs

Hello Josh,

What you are looking for is zero delay mode (ZDM). The LMk05318B does not support this. Please consider the LMK5B33216 which does support ZDM.

However, if you want to do some extra tuning loop and adjust the PH_OFFSET. I'll have to check, you may be able to this live to make the phases to align... however I'm not sure this is really what you want -- to have to manually intervene.

Please advise if you want to pursue PH_OFFSET updates.

73,

Timothy

Timothy,

Thanks for your reply.

To clarify what I'm trying to accomplish, I have a 10 MHz clock to which I want to apply a known, dynamically adjustable phase delay. I would prefer a granularity on the order of 1 ps, but the phase delay must be adjustable on the fly without resetting the PLL. The datasheet of the LMK05318B seemed to indicate that it was capable of this using the DPLL_REF_SYNC_PH_OFFSET register in conjunction with ZDM, but if it doesn't and the LMK5B33216 can instead meet my needs I will look at that.

I tried implementing ZDM on OUT7 of the LMK05318B as described in section 9.3.16 of the datasheet. However, attempting to apply a phase offset using the DPLL_REF_SYNC_PH_OFFSET doesn't seem to have any effect. If I understand your reply correctly, this would require an external tuning loop to accomplish? As you say, manual intervention is less than ideal, and if possible I'm looking for a device to which I can issue a correction and have the phase dynamically adjust on the fly.

Josh

Hi Josh,

Ok - I'll double check tomorrow about the DPLL_REF_SYNC_PH_OFFSET.

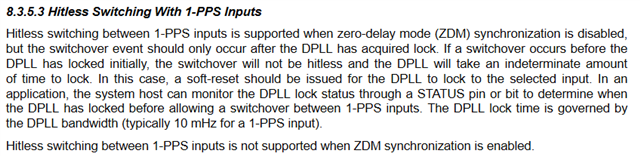

Note that ZDM on OUT7 of LMK05318B is not true ZDM -- it is an open loop synchronization. So for low frequency like 1 Hz/1-PPS - it is suitable but increasing frequency increases deviation.

Also, do you want more than one output aligned with input? OUT7 is the only output "aligned" with input.

On the LMK5B33216 I'm pretty sure that update is immediate.

73,

Timothy

So it sounds like the LMK5B33216 would better suit our needs than the LMK0513B.

No, we only need one output, so just OUT7 would have worked if the LMK0513B could do what we needed it to.

In regards to the LMK5B33216, do you know if the datasheet correctly describes how to put the device into ZDM mode and apply manual phase corrections?

Josh

Your support engineer is out of the office today, you can expect a response tomorrow

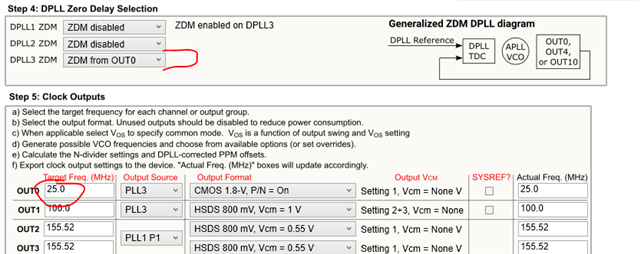

The LMK5B TICS Pro software allows you to setup the ZDM fairly easily.

Select the output for ZDM. Simplest ZDM has input and output frequency the same. But technically you can do ZDM with output frequencies higher than input.

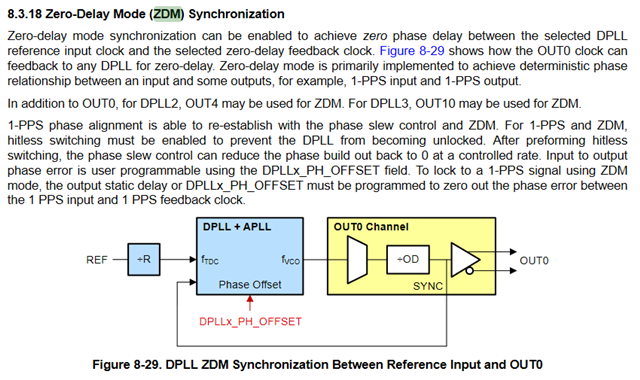

This Multi-Clock Synchronization app note talks a bit about ZDM generally and gives two rules for ZDM:

First Rule, the GCD Between Input and Output Frequency must Equal Input Frequency

Second Rule, Lowest Output Frequency Requiring Determinism used for ZDM Feedback

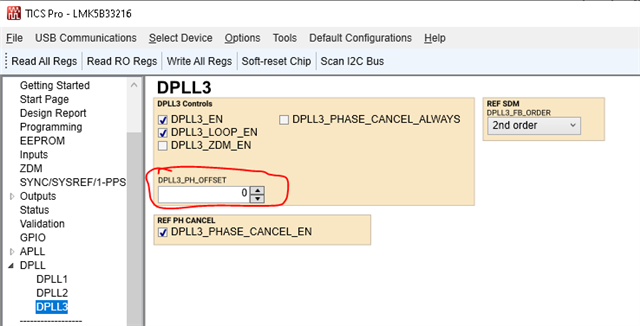

Adjust phase here on the DPLLx page by updating DPLLx_PH_OFFSET. At this time we don't have a calculator for time <--> DPLLx_PH_OFFSET number.

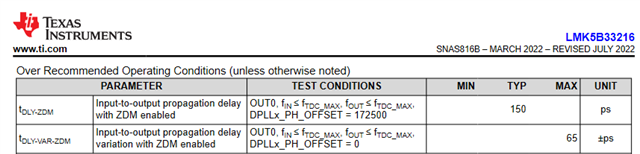

We do have some specs and basic info in the datasheet.