hello,

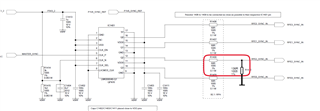

my circuit design as below for your reference; now the VDDO is 1v8, the Q2 connect with FPGA I/O via two resistors dividing voltage (because the FPGA I/O input voltage scope is 1V-1.8V) ,I want to keep the FPGA input voltage at about 1.2V.

my question is whether I can use the Q2 output in this way?

if no, please give your reason and other proposal.

if yes, what is the current of case? the Q2 current driver capability is enough or not?please help to calculate the values ,i don't find the output current parameter in datasheet.