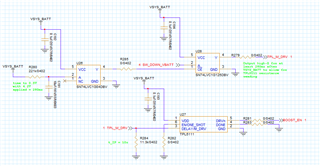

Other Parts Discussed in Thread: SN74LVC1G125, SN74LVC1G04,

My use case is this:

EN/ONE_SHOT = GND (one shot mode). TPL5111 M_DRV held high by toggle switch (not momentary) so that DRVn is high all the time (keeps load switch enabled to power the system). When switch is toggled, M_DRV will go low, and DRVn will go low after the timer period expires (turning off load switch). Effectively, this is a delayed shutdown circuit.

What I am worried about is the timer conversion time, if M_DRV is held high at boot, or comes high before the conversion time t_Rext has elapsed, what will that do to the stored timer interval period?