Other Parts Discussed in Thread: CDCE6214

Dear Expert

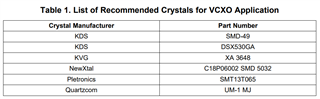

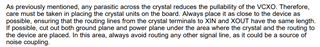

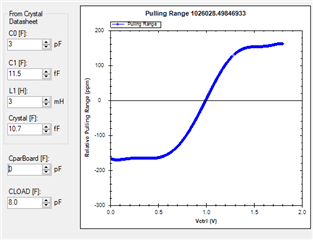

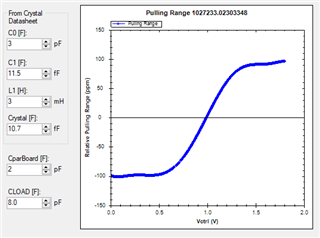

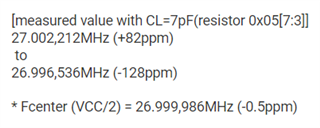

Regarding the application issue of CDCE913 VCXO, based on the previous factory response, we have further debugged it, but it is still unable to meet the requirements of plus or minus 150PPM. Now that the recommended crystal oscillator GSX530GA in the SCAA085 document has been replaced, it still cannot meet the requirements. The pulling range test result is+29PPM~+216PPM. Why is the pulling range all positive? And the maximum and minimum range cannot reach 300PPM. Please help to continue analyzing the problem. Thank you!