Hi,

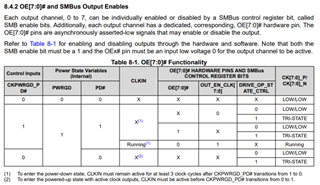

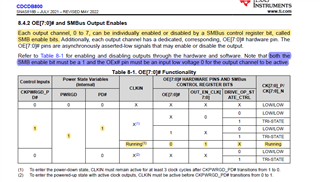

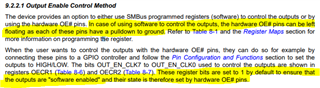

For clock buffer CDCDB800, we can enable the clk out either by enabling the SMB enable bit(OUT_EN_CLK) or via OE# hardware pins.

a) If I intend to use SM Bus register instead of hardware pins, will the register setting retain after power off?

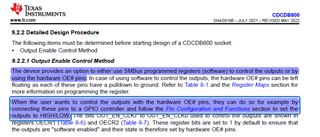

b) Do we need both OE# pin and OUT_EN_CLK to to enable clock out?

c) In its datasheet it is specified that OE# pin has to be connected to a microcontroller GPIO pin to set HIGH or LOW. Can we use a pull up or pull down resistor instead of microcontroller?

Thanks and Regards,

Shekha Shoukath