I'm using LMK04808.

I would like to inquire because I have any questions regarding the operation of LMK04808.

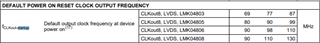

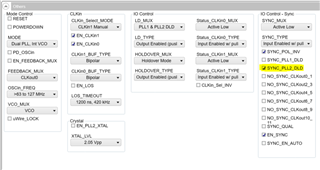

The LMK04808 configuration is used as a Single PLL mode configuration (PLL2, Internal VCO).

OSCin is used for PLL reference input.

All 12 channels from LMK04808 clock output 0 to 11 are in use.

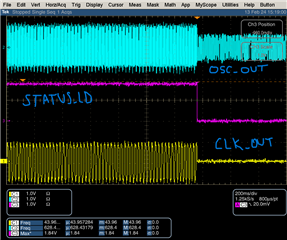

After turning on the power to LMK04808, the clock is output well at the set value.

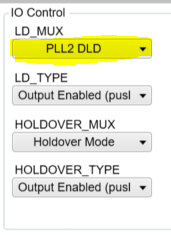

In this state, the LMK04808 clock output is normal even without inputting the PLL reference clock (OSCin) (except for ch 6 and 7).

I understand that ch6 and 7 are not output because they are divide type output from OSCin.

Except for ch6 and ch7, the remaining channels are continuously output even without inputting the PLL reference clock (OSCin).

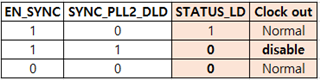

I would like to know why clock output continues even if the PLL reference clock (OSCin) is not input after PLL Lock.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.