Other Parts Discussed in Thread: CLOCKPRO

Hello,Team,

I have questions about CDCE913PW

Q1

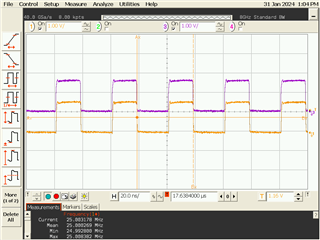

Is there any latency between Y1 to Y2/Y3, when this devide is set to use Y1,Y2,Y3 from Pdiv1?

or in that case,using Y1 with Pdiv1,Y2 with Pdiv2,Y3 with Pdiv3,which is the same out Freq,is there any latency between Y1 to Y2/Y3?

And is that possible that using Y1 and Y2/Y3 to output for RCKI for SRC(SRC4184IPAGT) as SYNC?

Q2

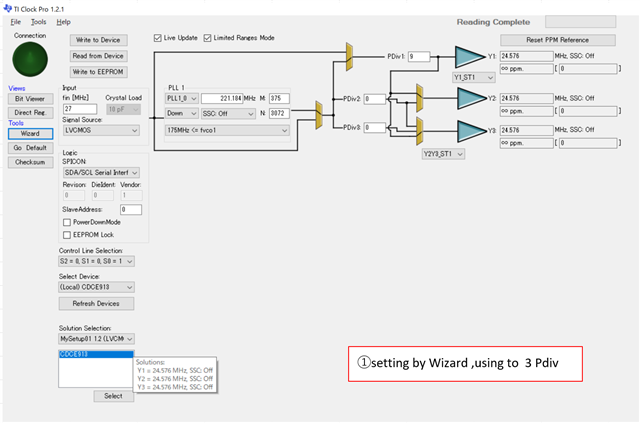

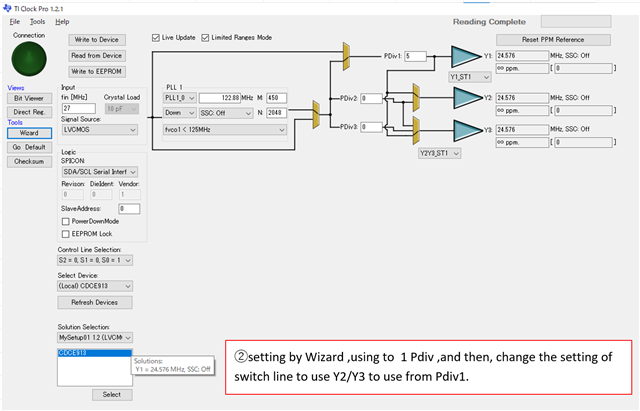

Why is there difference about M,N,freq for PLL,in Clock Pro between when using only Y1 and when using Y1/Y2/Y3,in spite of using the same Inclock and the same out Freq setting.

I guess there is no change to set Y2/Y3 to use from Pdiv1 which is used for Y1 setting.

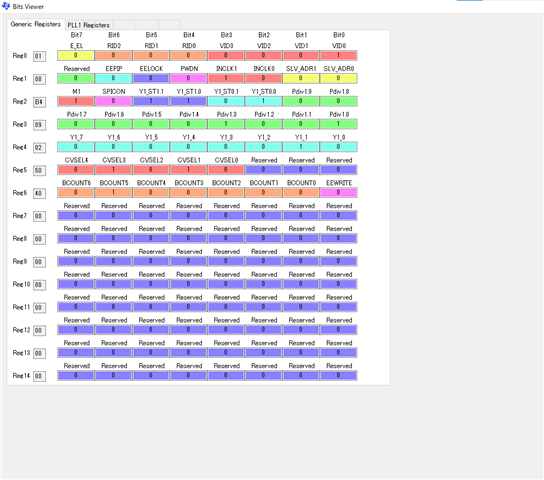

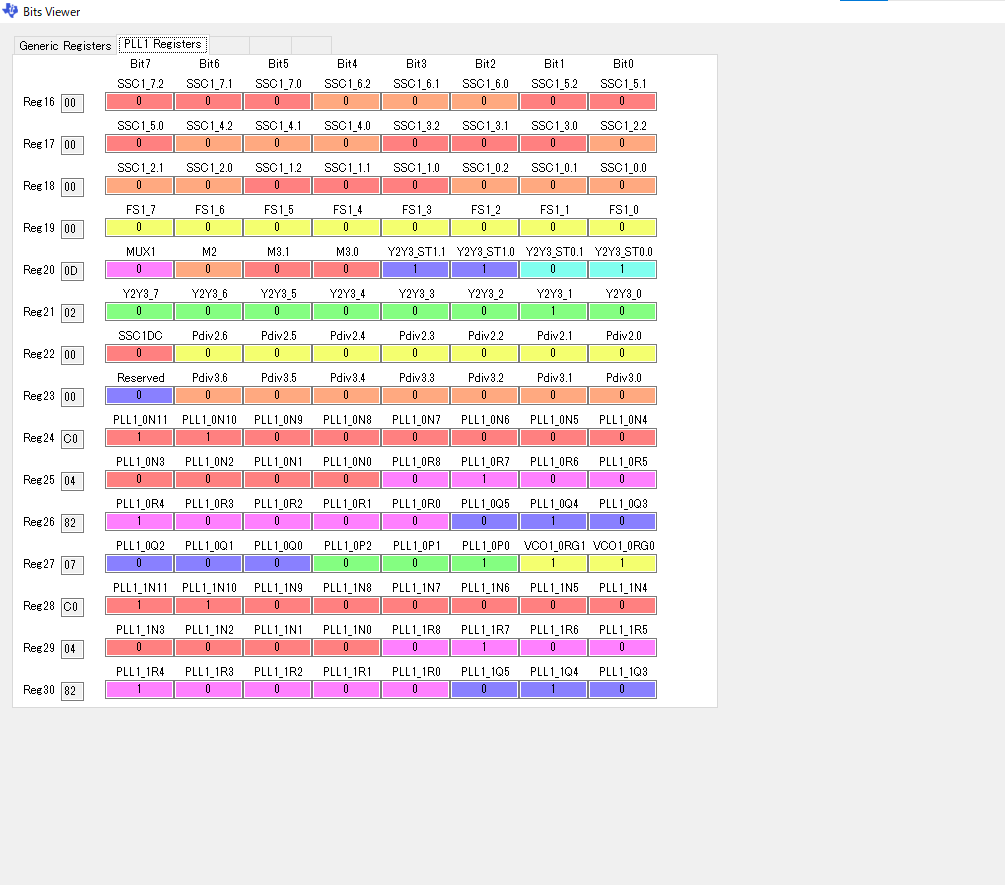

Anyway, in this case that this device to use Y1/Y2/Y3 the same freq and the same Pdiv,i can use reg setting refer to BitViewer in Clock Pro,is that OK?

Q3

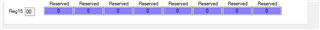

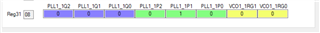

In Clock Pro, why i cannot see reg15 nad 31 in BitViewer?

Q4

If i set reg"EEWRITE" to 1 for save the data to memory, is reg"EELOCK" set to 1 immediately without operating reg"EELOCK" setting?

Thank you for your support