Hello,

What is the max input voltage to the LMK04832-SP when it is not powered? Is there also a frequency dependency when powered off?

There is a note in the datasheet that specifies the unpowered state of the device:

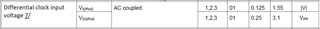

"(2) When the device is in an unpowered state, the clock input pins (CLKinX/FinX and OSCin) can accept AC-coupled signals up to

±400mV. The absolute limit for an unpowered device input while AC-coupled is determined by the ±5mA (RMS) current limit for the

pins. The ±5mA (RMS) current limit for AC-coupled clock inputs is satisfied across operating junction temperature by a ±400mV

signal coupled through 0.01μF capacitance across allowed operating frequencies. Larger"

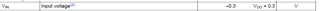

Though it also states the max input voltage is VDD+0.3V so if VDD = 0V, then Max input voltage is 0.3V

For my application, the LMK will receive a sine signal on Fin0. Fin0* is ac-coupled to ground.

Thanks!