Other Parts Discussed in Thread: TLC555, NE555

Tool/software:

Hi TI service team,

For LM555CMMX timer application in my system, I have questions about the functional operation want to consult with you.

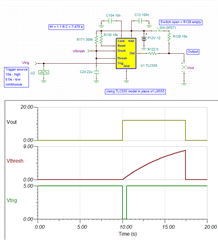

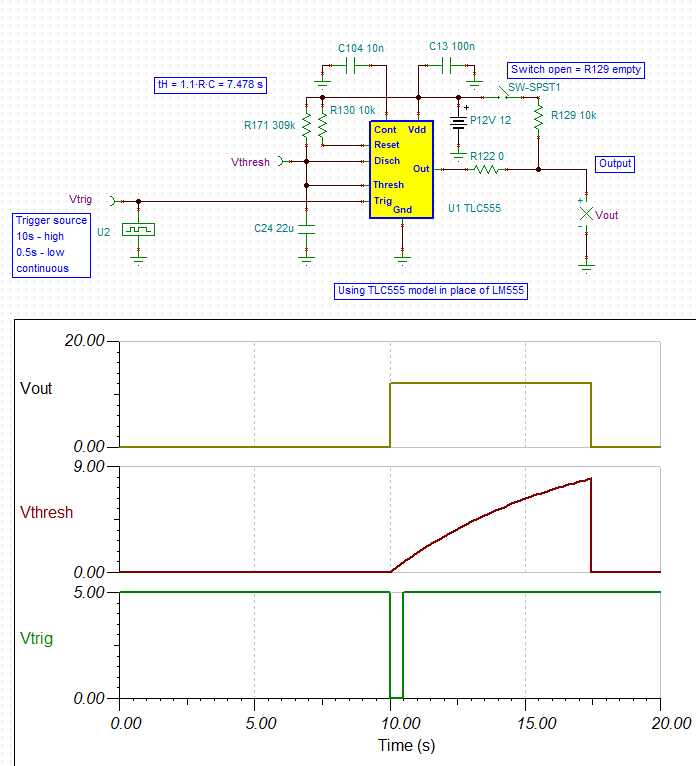

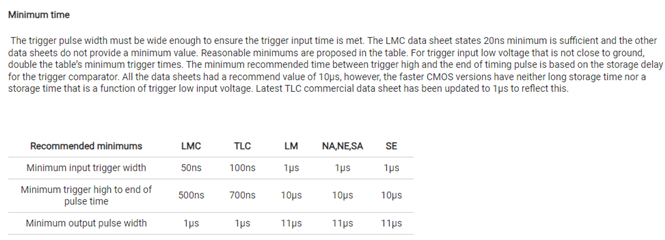

For my requirements, I want to add a timer with LM555 by RC delay calculation between TRIGGER_N pin to the OUTPUT pin, and I only need MONOSTABLE behavior without oscillator output status.

Therefore, I set R=309K*C=22uF delay in THRESHOLD pin for timing delay with about 7s (1.1*R*C).

How does the LM555 behave? Am my understanding correct with below descriptions?

If I'm wrong, please help to correct and give advice of right mechanism with this IC.

When TRIGGER_N is higher than 1/3*VCC, OUTPUT pin will go H after THRESHOLD charge capacitor up to 2/3*VCC (~7s). (???)

When TRIGGER_N is lower than 1/3*VCC, OUTPUT pin will go L after THRESHOLD discharge capacitor low to 2/3*VCC (~7s). (???)