Tool/software:

Hi TI,

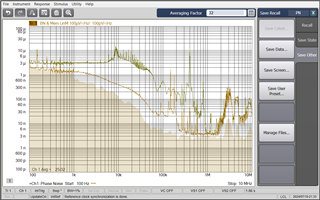

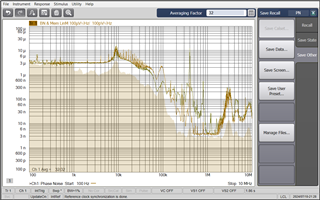

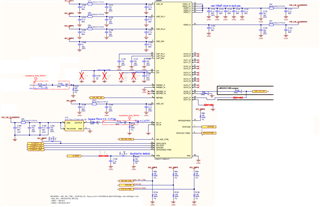

I am currently using LMK05318B in our application design, having

- external TCXO with 40MHz

- external PRIREF 25MHz

In principial this is working fine and I am getting a suitable lock.

When reading out the status registers, also everything is locked.

When reading out the interrupt registers,

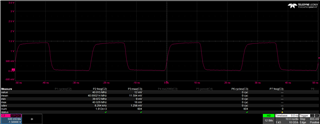

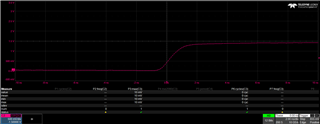

- R19 bit0 (LOS_XO_INTR) is set, even after clearing it

- R20 bit3 (REFSWITCH_INTR) is set, even after clearing it

I am guessing there is an intermitting and short term issue occuring, which is not visible at the status bits but visible at the interupt bits.

Looks like XO input and Priref input are not qualified as valid, for a short time.

Customer would like to confirm what is the mistake may cause this issue? can you help to check?

Please see attached tcs file.

P.S: Running the same settings at the EVM board does not lead to this error and everything is working as expected.

Thanks & Regards

PF