Part Number: LMK04828BEVM

Other Parts Discussed in Thread: LMK04828, LMK04826

Tool/software:

hello,

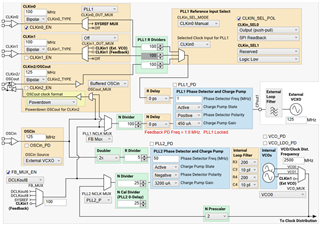

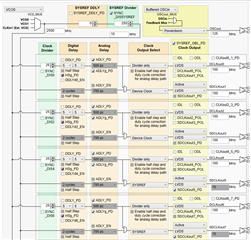

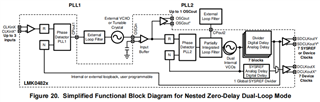

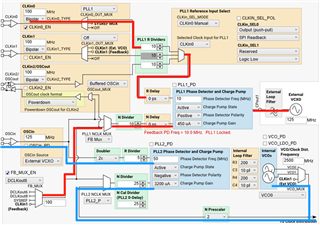

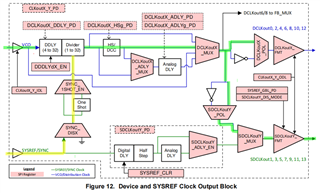

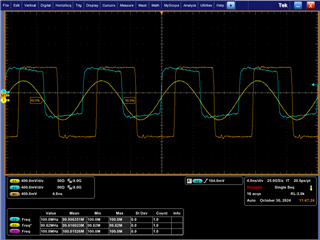

Our current application is to synchronize all the input and output clocks of the LMK04828, and the phases are aligned after the sync signal is controlled;

Now there are 3 questions : 1. The input and output are not synchronized, and the phase difference is also not fixed (it will change after each power-on restart). 2. After the sync signal is controlled, the waveform can be seen to flicker on the oscilloscope, but there is no change. 3. Is there a timing requirement when configuring registers for SPI?

【Current configuration】