- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi,

The input frequency to clock buffer is 1800MHz and we plan to connect CLKOUT pins to FPGA and set them at output frequency of 225MHz.

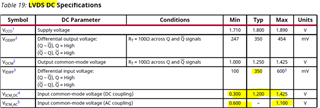

The CLKOUT pins seem to be similar to CML standard. FPGA can support LVDS as below:

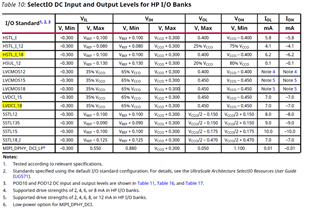

It also supports below highlighted differential standards.

So, can you please share which standard to use at FPGA's input side to meet CLKOUT's output standard?

Also pls recommend what type of termination needs to be used between these two interface standards?

Thanks

Hi Noel,

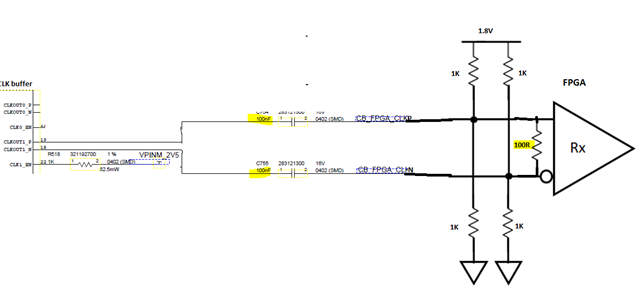

Do you mean like this?

100 ohm parallel termination between P & N signals. And external biasing termination resistors at RX end?

Hi Noel,

I will confirm with FPGA vendor on this.

However can you share from clock buffer's perspective, if 100-ohm differential between P & N is ok instead of the 50-ohm termination (presumably to GND) that you were suggesting?