Other Parts Discussed in Thread: CDCLVP1204

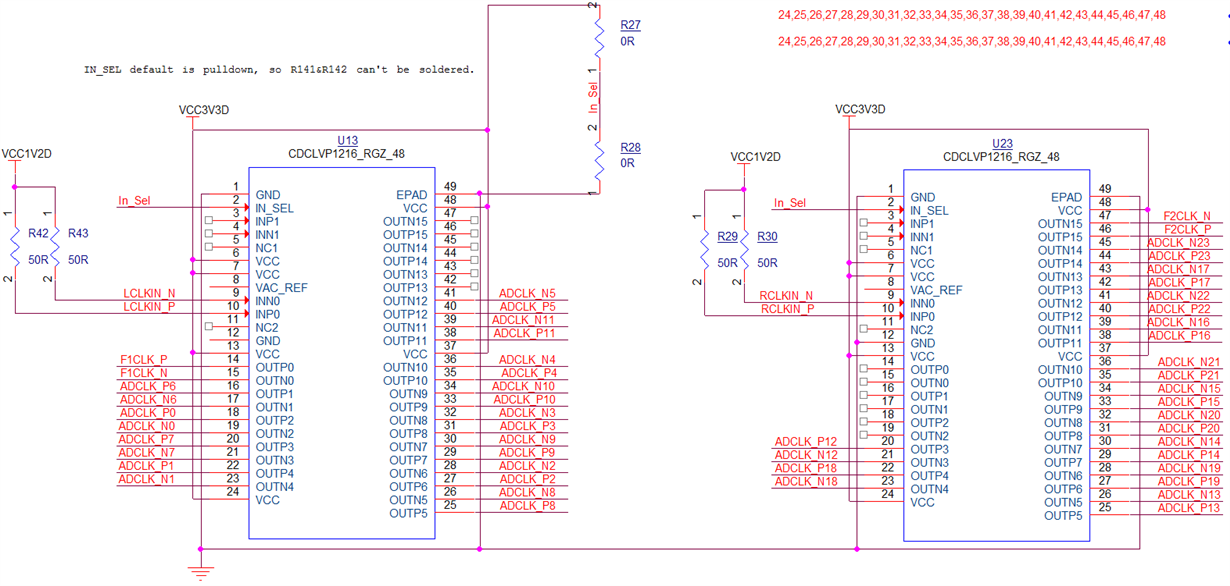

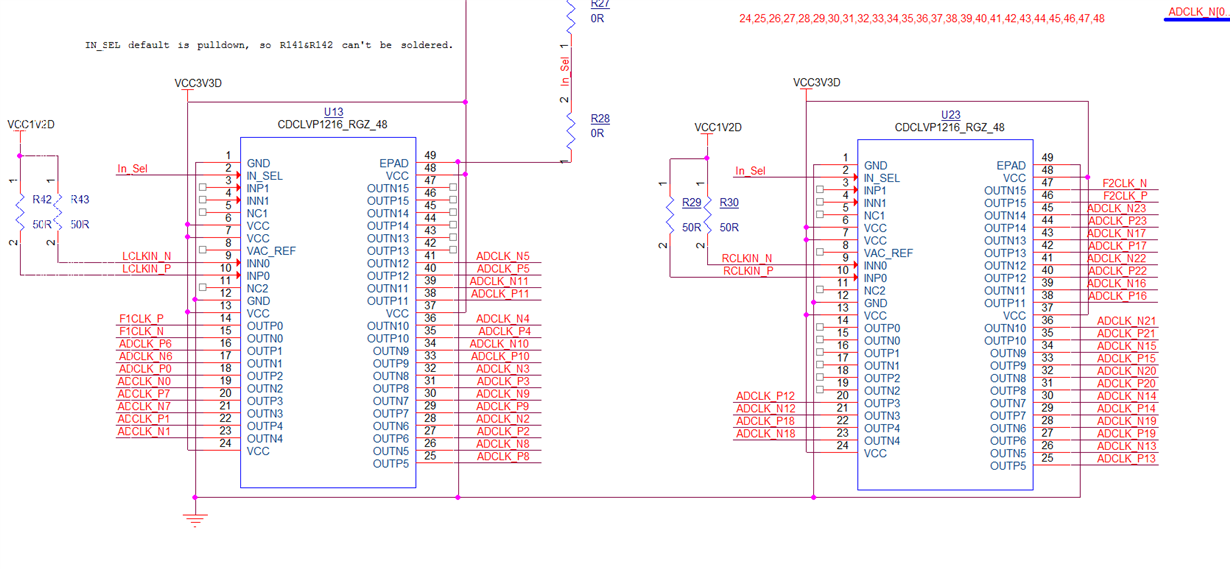

We are using CDCLVP1216 to replace ON-Semi's NB100LVEP224. We used board provided 1.2V to pull-up 50 ohm on each input leg to couple LVPECL clock when we used NB100LVEP224. Now we want to use same method on CDClvp1216, however, how to process pin Vac_ref, can we leave it float? I attach our schematic design here, please help us checking with it.