Hi :

Need kind help on CDCE62005 design.

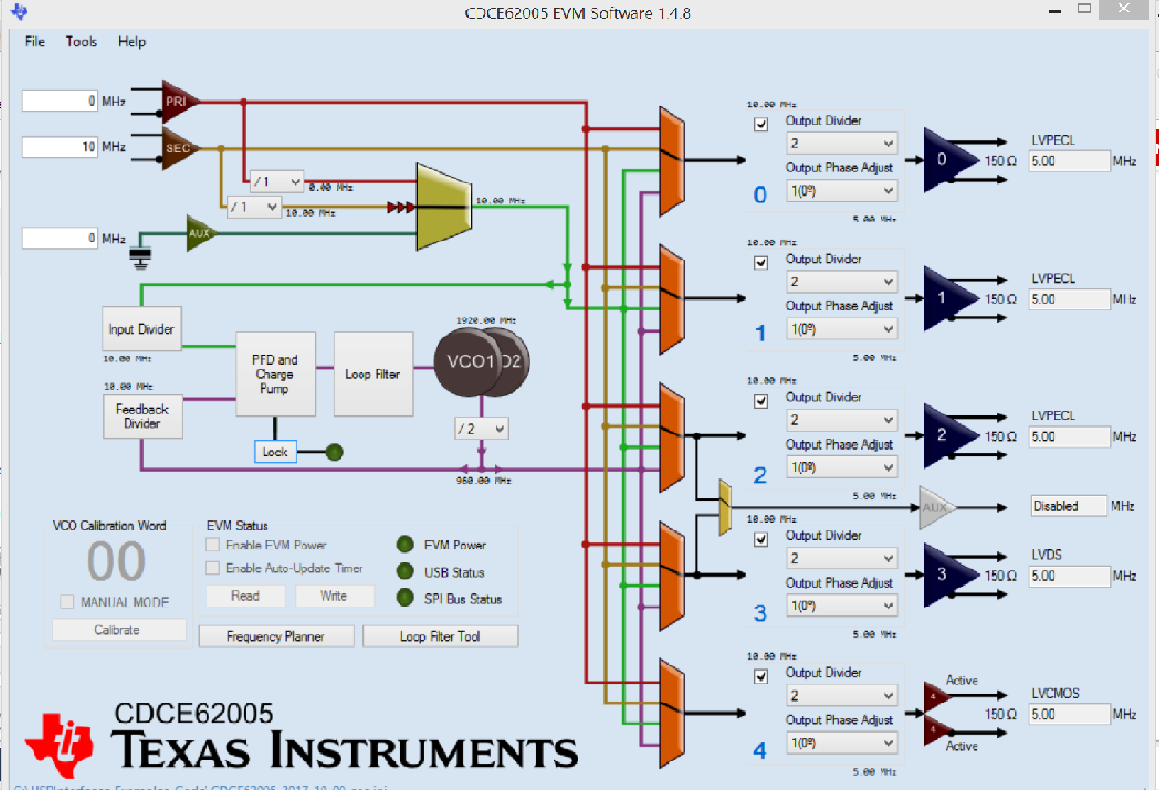

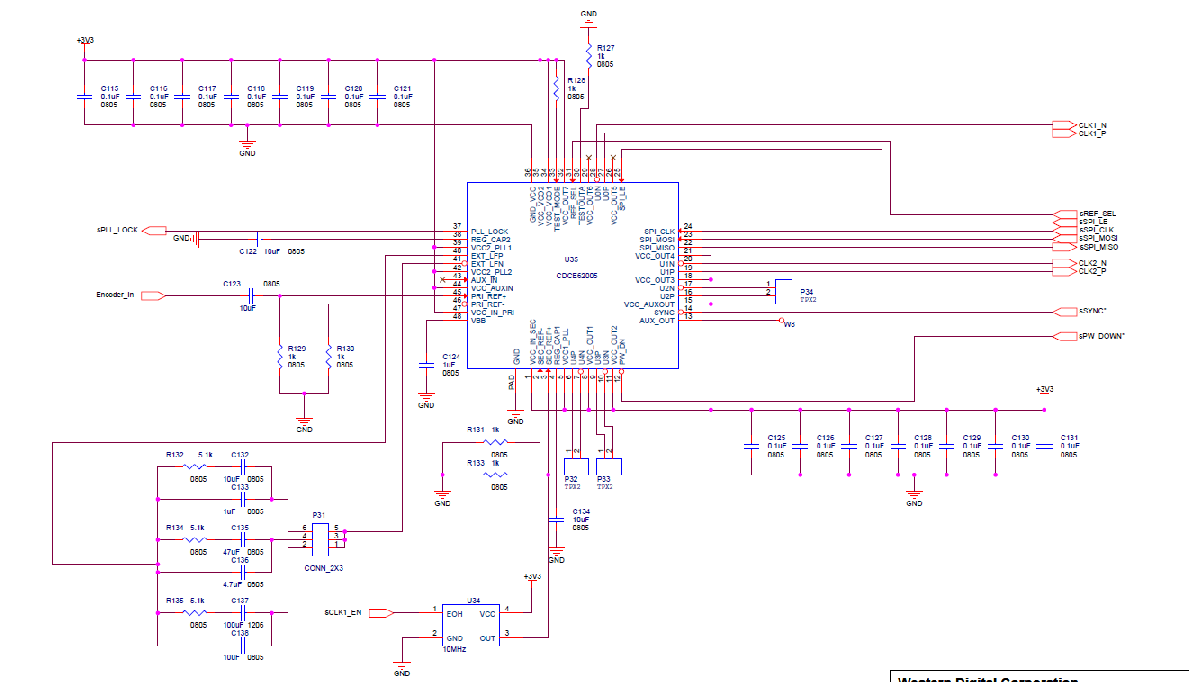

I use 10MHz reference clock for PRI_REF and SEC_REF, and use VC++ Interface code to set up registers, I tried many register configurations, one of the register setting is as below:

Reg_0 0xEB840000

Reg_1 0xEB840021

Reg_2 0xEB860302

Reg_3 0xEB860303

Reg_4 0xEB860334

Reg_5 0x800C6E45

Reg_6 0x84BE19C6

Reg_7 0xFD90FBA7

Reg_8 0x200099F8

After writing these registers, I can read back the same setting through sSPI_MISO on all registers, which tells me SPI interface is working.

The purpose of the design is to see two output clocks on U0 and U1 generated from PRI_REF input. But, I couldn't see clock signals on any output ports.

I don't know if it's hardware problem or not. Can anyone help me check the setting or give any suggestions?

Thank you very much in advance!