Other Parts Discussed in Thread: DAC38J84, DAC37J84

Hi,

after reading several datasheet and app notes I still got a few questions about how to generate the right SYSREF and SYNC signals.

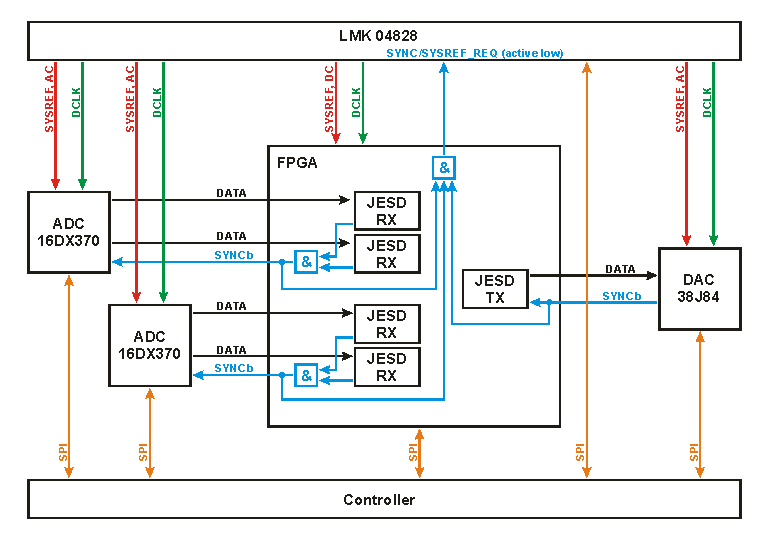

We'd like to use subclass 1 for deterministic delays between the ADCs and the DAC in our system:

(Nov. 20: edited image)

During the initialisation of the LMK, the internal dividers are synchronised by toggling the SYNC polarity register bit (SYNC_POL). Following, the divider synchronisation is disabled (SYNC_DISxx). Now, after the device clocks are stable, we initialise the ADCs, the JESD IP cores and the DAC.

By pulling the SYNCb line low, each JESD receiver can cause the corresponding JESD transmitter to send the synchronisation sequence -- but when and how should we request the LMK to generate the SYSREF pulse(s) before?

- For example, we could trigger a SYSREF pulse over SPI, the same way we did during the initialisation and internal synchronisation.

- We even could repeat this regularly and check the devices for re-synchronisation.

- Alternatively, we could also conjunct all SYNCb outputs (from DAC and JESD RX IP cores) into a common SYNCb (to ADCs, JESD TX IP core and LMK) for an automatic SYSREF generation on SYNC request. But in every diagram I've seen the SYSREF is over before SYNCb is pulled low, so maybe we'd need to delay the SYNCb to the ADCs and the JESD TX IP core.

So, is there some common or preferred method for triggering SYSREF generation?

Also, I found there are several modes of SYSREF generation (one pulse, multiple pulses) and acceptance (all pulses, first pulse, second puls, all pulses after the first,...) but I did not find any recommendation which one to use and why.

Best regards,

Michael.