Part Number: LMK04828

Other Parts Discussed in Thread: LMX2594, TIDA-01023, LMK04832

Hi All,

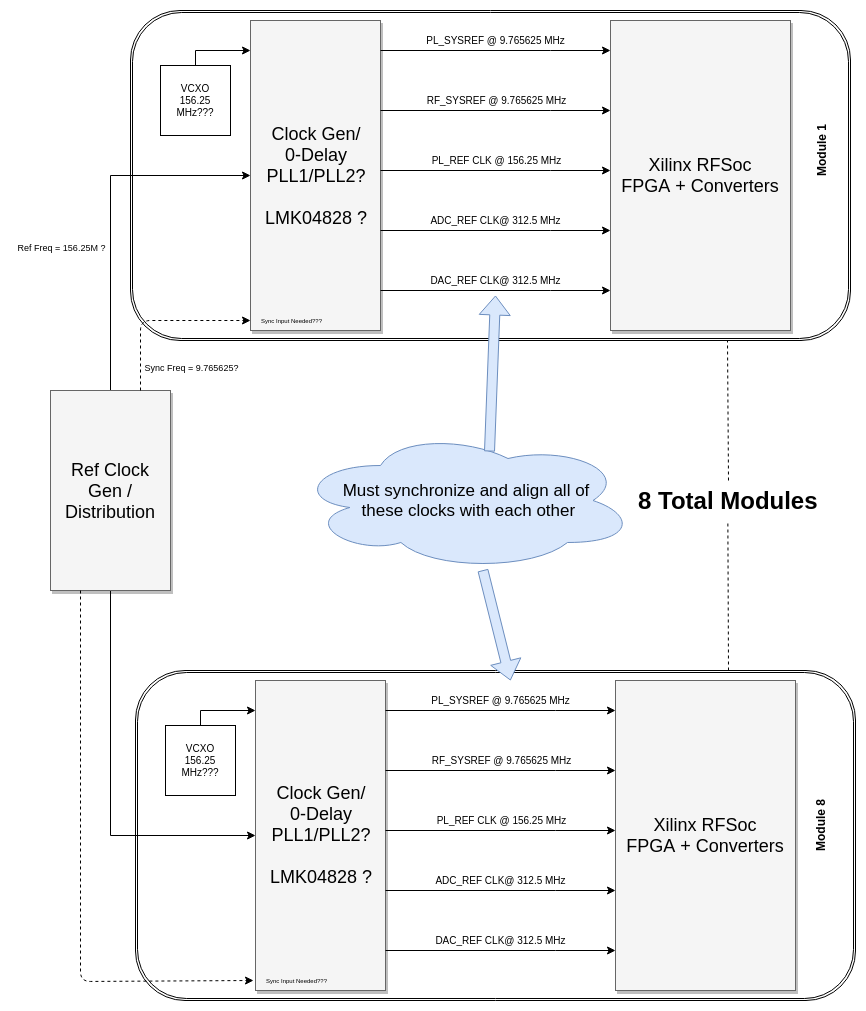

We're designing a system that will have 8 Xilinx RFSoc modules that will all need to be synchronized. I've been told by Xilinx reps that the converter synchronization structure for the RFSoc behaves as a JESD204B converter does. The 8 modules (each with an RFSoc) will be mounted on a single, central compute board that will be responsible for distributing common signals and clocks.

The preliminary design needs to have clocks in the 156.25 MHz family and the module RF clock frequencies are:

- ADC & DAC REF Clk = 312.5 MHz

- PL REF Clk = 156.25 MHz

- PL_SYSREF & RF_SYSREF = 9.765625 MHz (this frequency must be < 10 MHz per Xilinx).

The requirement is to have all of these individual clocks synchronized and phase aligned not only in the module, but also across all modules. The target is < 50 ps of jitter with the minimal amount of phase skew possible. I've read multiple posts on this forum regarding the LMK04828 in zero-delay mode and I believe this is possibly the best solution, but I'm not sure if these frequencies are possible and what zero-delay mode would be best to use. I've been using the TICS pro software but it will not allow me to hit these frequencies and I'm not sure of the best VCXO frequency to use. Any thoughts and values for these would be awesome.

Below is an overview diagram of the current thoughts:

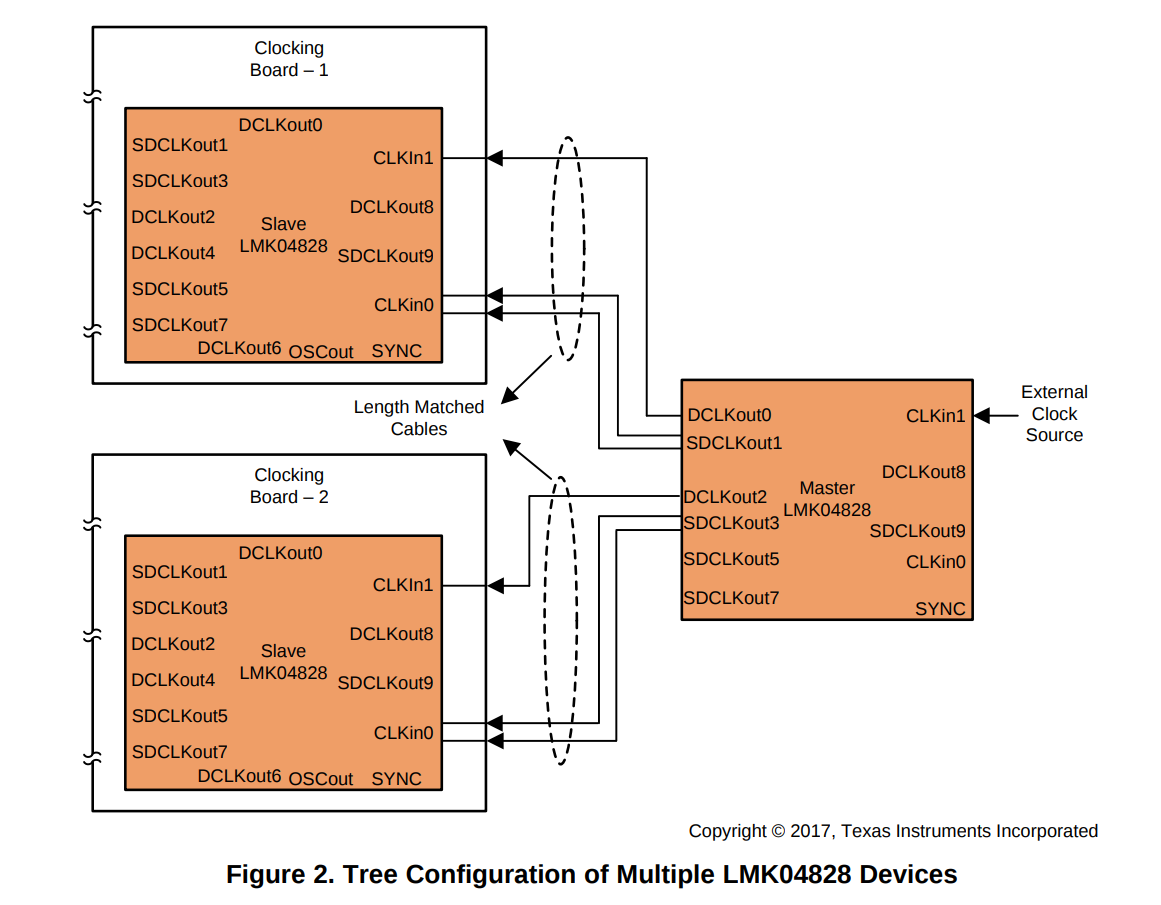

If all LMK04828 modules are in zero-delay mode and are being fed by the same reference clock, is it necessary to have an input sync signal?

Thanks for the time in advance,

-Jim