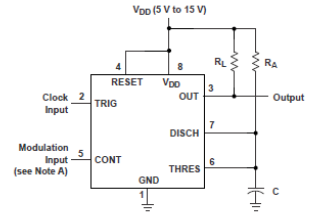

- How does the PWM example in the data sheet work?

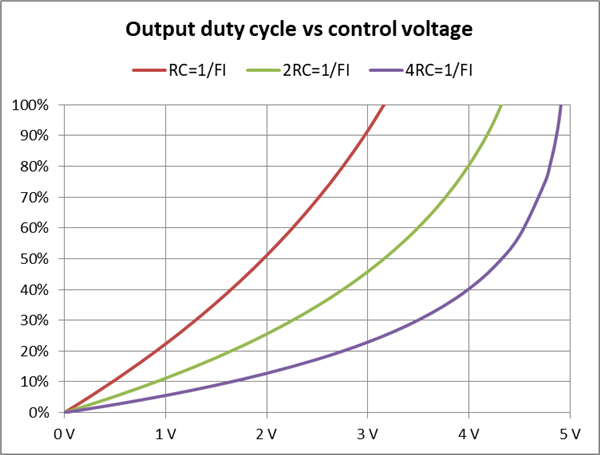

- What are the limitations of the data sheet PWM example?

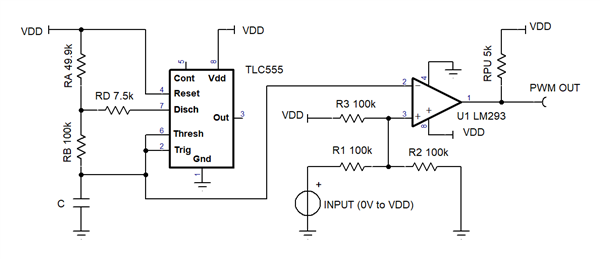

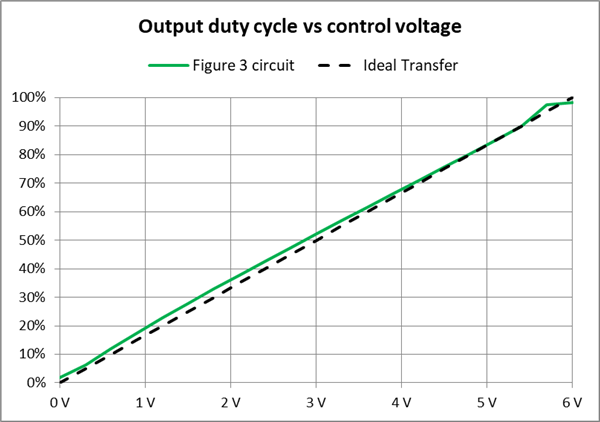

- Is there a way to improve linearity and duty cycle range?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.