Other Parts Discussed in Thread: DAC38J84,

Hi team,

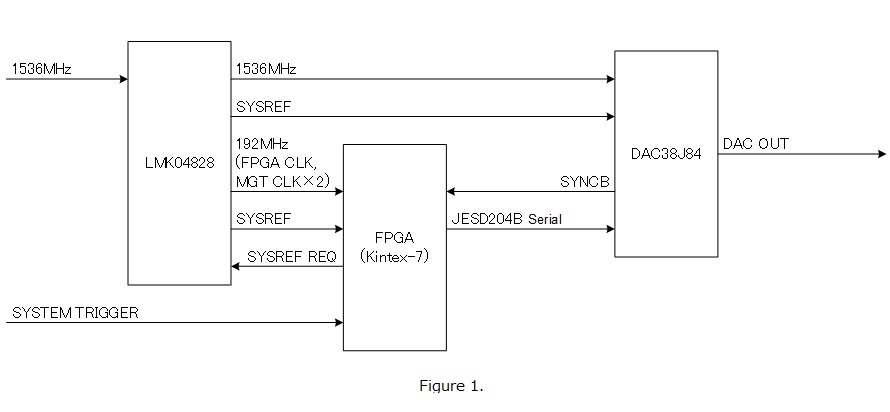

We are currently using a Xilinx FPGA Kintex-7 and a Xilinx JESD204 IP core to output analog signals with a TI DAC (DAC38J84).

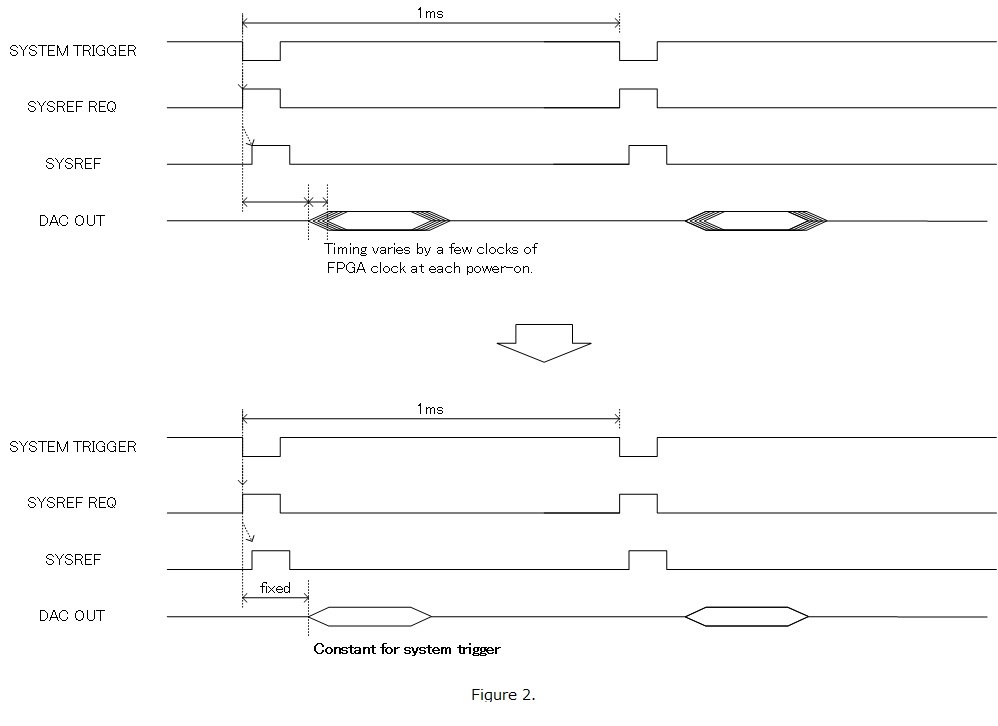

For example, the FPGA receives triggers every 1ms and needs to output an analog signal at that timing, but the analog output timing fluctuates between a few clocks in the FPGA clock every time the power supply is turned on.

However, the analog output timing varies between several clocks at each power supply startup, and we would like to output analog signals at the same timing.

We are using the JESD204B in Subclass 1, but since we do not have much experience with Subclass 1 and do not understand the operation of the JESD204B, we would like to ask you about the following

"Operating Conditions"

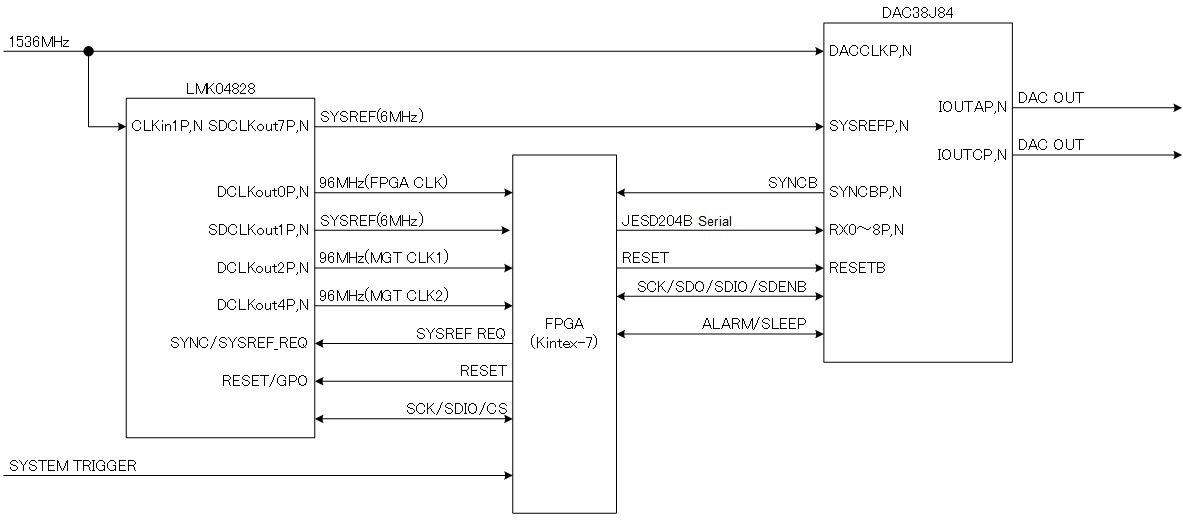

DAC is DAC38J84 and LMK04828 is used for clock and SYSREF generation.

LMK04828 CLKin1/Fin/FBCLKin (pins 34, 35) with 1536MHz input to LMK04828, 1536MHz for DAC, 1536MHz divided by 1536MHz, 192MHz to FPGA and SYSREF (8MHz) to DAC and FPGA (supplied by Pulser to DAC and FPGA). (Figure1)

The FPGA is a Xilinx Kintex-7 with a JESD204 Subclass1 IP core.

"Questions"

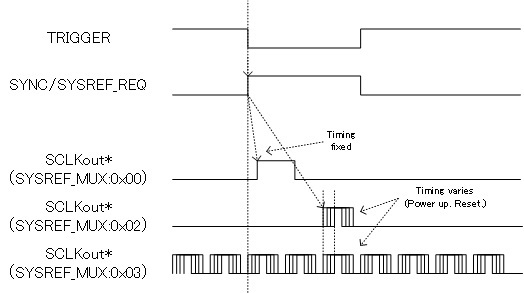

Q1) Is it possible to adjust the phase of SYSREF to the trigger timing that is synchronized with 1ms as shown in the figure2?

In short, I would like to use the trigger as SYSREF_REQ signal and make it the same timing (same delay).

The trigger timing is synchronized with the clock, but the phase relationship with SYSREF changes every time because the timing is different at each startup.

However, since the timing is synchronized with the entire system, the phase relationship is constant after startup. The timing of the trigger and SYSREF does not change.

Q2) I have a question about the operation of the DAC.

For example, if the register is fixed to a certain setting, is the internal delay in the DAC constant or does it fluctuate?

For example, is the internal delay in the DAC for a certain register setting constant, or is there a factor that varies?

It may have something to do with the IP core of the FPGA, but I would like to know if it is possible to output analog signals without any fluctuation in the trigger timing at each startup.

Q3) I have a question about the operation of the DAC.

Is the relationship (delay) between the SYNC signal output from the DAC and the DAC analog signal output constant?

I believe that the timing between FPGA and DAC can only be ascertained by the SYNC signal from the DAC, but I thought that if the relationship between the SYNC and DAC analog signal output is different, it may be difficult to keep the timing constant.

If you have any other points to note (settings, usage, etc.), I would appreciate it if you could give me some advice.

Best regards,

T.Karita