Other Parts Discussed in Thread: AFE58JD18

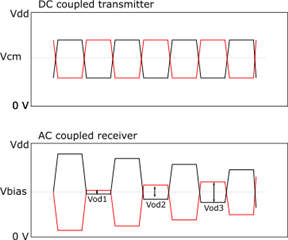

Looking at the output of the LMK04821 SDCLKout using a differential probe (10:1) I can see the following.

The DCLKout outputs look ok, with a nice waveform. The SDCLKout outputs that are providing the 16.6MHz sysref

look "terrible". Is there something I should set differently?

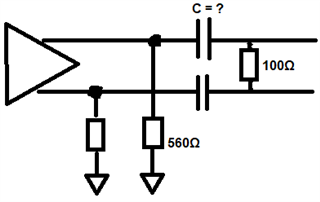

At the outputs of the LMK04821 we have placed 560R shunts, then AC-coupled to the destination and have a 100R termination there (which is actually the sysref input of the AFE58JD18).

Any idea?

Kind Regards,

Ed