Other Parts Discussed in Thread: DAC38RF89

Hi team,

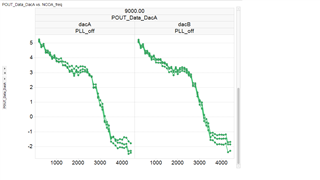

My customer is trying to evaluate DAC38RF89 with DAC38RF89EVM + TSW14J56EVM.

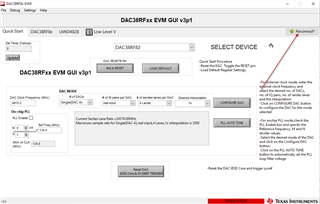

They will use High Speed Data Converter Pro GUI and DAC38RF8x EVM GUI.

However, DAC38RF89EVM connection to PC fails on the above GUIs.

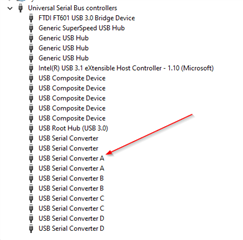

My customer noticed that the windows device manager doesn't recognize the device, or the appropriate driver is missing.

TSW14J56EVM connection is successful.

My customer tried to find the device installer on TI.com, but they didn't find it.

Could you please help me to address this issue?

Best regards,

Itoh