Part Number: EVMK2G

Other Parts Discussed in Thread: PCM1865, AUDK2G, TLV320AIC31

Tool/software: TI-RTOS

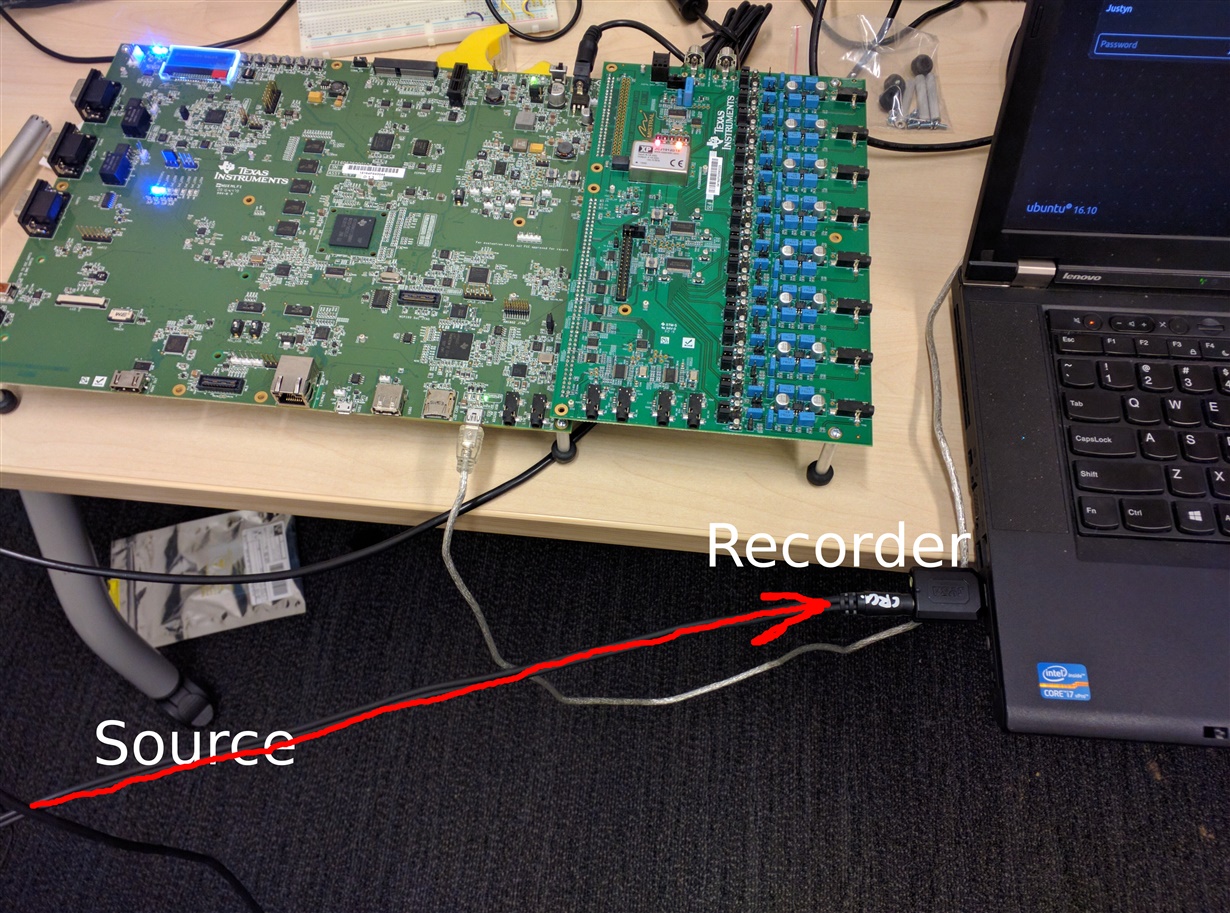

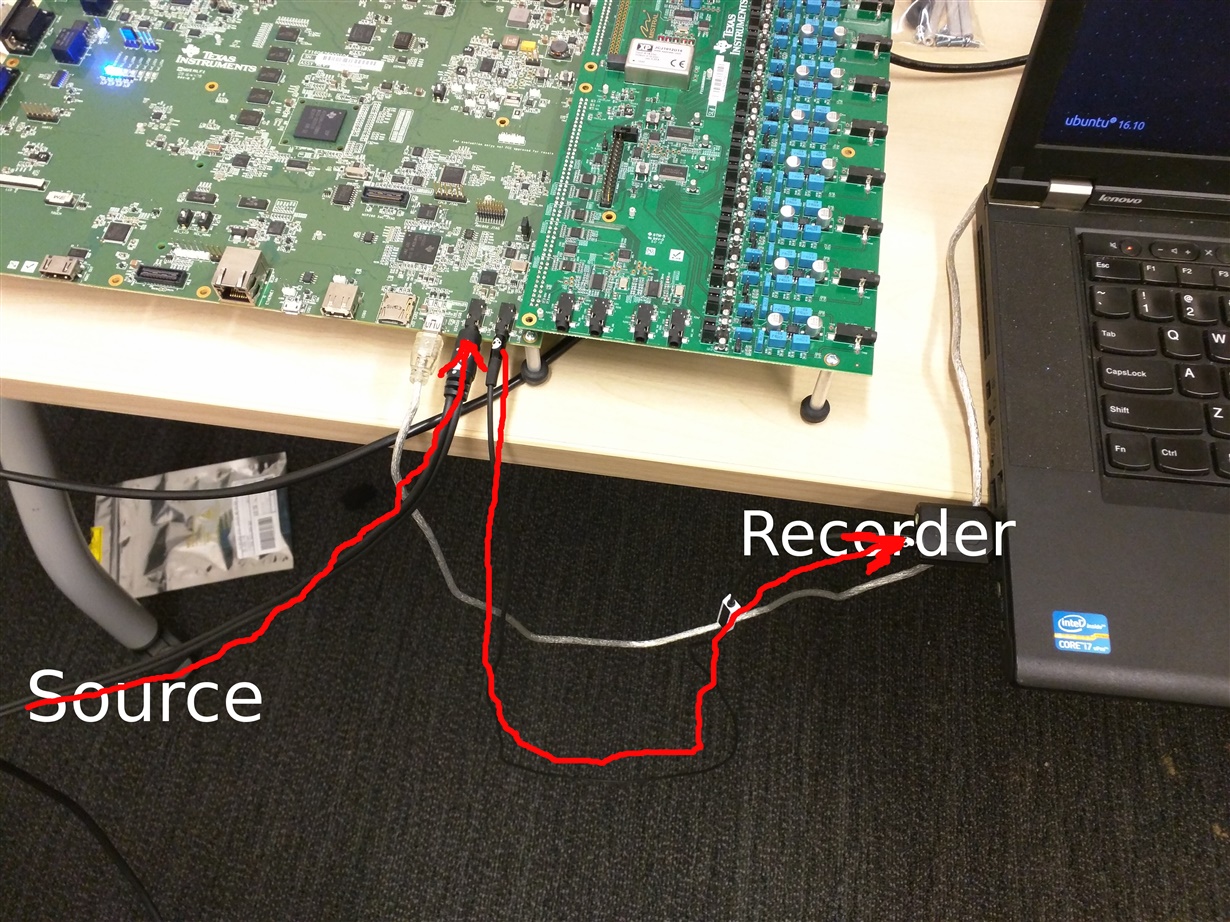

I've tried searching the forums for this problem, but it seems that anything similar is for another platform, so I decided to make a post regarding the EVMK2G specifically.

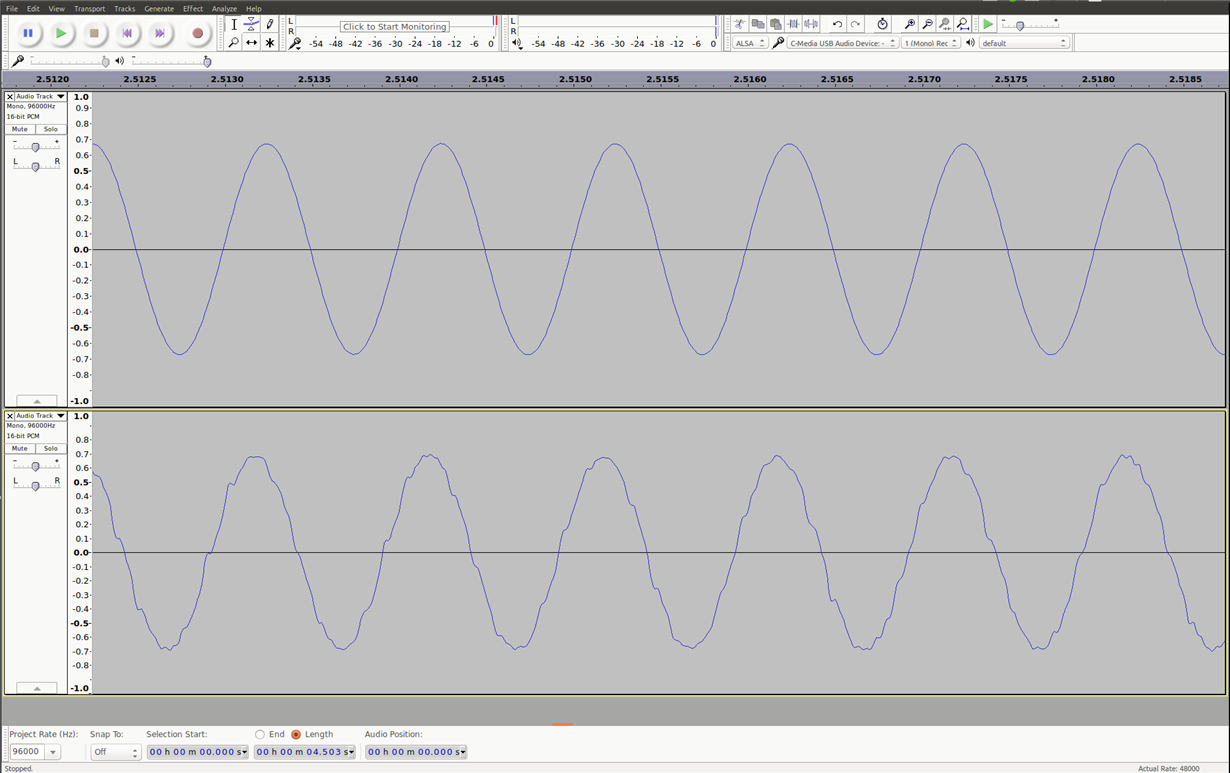

I'm using the 3.01 TI-RTOS SDK, and only need to get the mcasp loopback example working (the AIC31_Stereo_Loopback example). As of now, the loopback works, but I can't change any parameters such as the codec gain, or sample rate. It looks like AIC31SampleRateConfig never gets called in Aic31.c (around line 525 -> 527 -> 529) because it fails the branch `if (ICodec_OpMode_MASTER == instHandle->acOpMode)`.

There's a #ifdef that sets up the codec's opmode in the parameter structure in Aic31.c line 85. In the makefile MCASP_MASTER is defined. This is the code:

const Aic31_Params Aic31_PARAMS = {

ICodec_CodecType_AIC31, /* acType */

ICodec_ControlBusType_I2C, /* acControlBusType */

"NONE", /* acCtrlBusName */

#if defined (MCASP_MASTER)

ICodec_OpMode_SLAVE, /* acOpMode */

#else // MCASP is slave

ICodec_OpMode_MASTER, /* acOpMode */

#endif

#if defined DSP_MODE

ICodec_DataType_DSP,

(uint32_t)ICodec_SlotWidth_16, /* acSlotWidth */

#else

ICodec_DataType_I2S, /* acSerialDataType */

(uint32_t)ICodec_SlotWidth_32, /* acSlotWidth */

#endif

ICodec_DataPath_TXRX, /* acDataPath */

0, /* isRxTxClockIndependent */

};

Is this line correct? It's what's preventing the code from making the sample rate configuration call.

#if defined (MCASP_MASTER) ICodec_OpMode_SLAVE,

It might be right, but it just looks like a red flag to me. However, if I switch this around, then the loopback no longer works. I hear nothing; and the Audio_echo_Task callback is never fired.

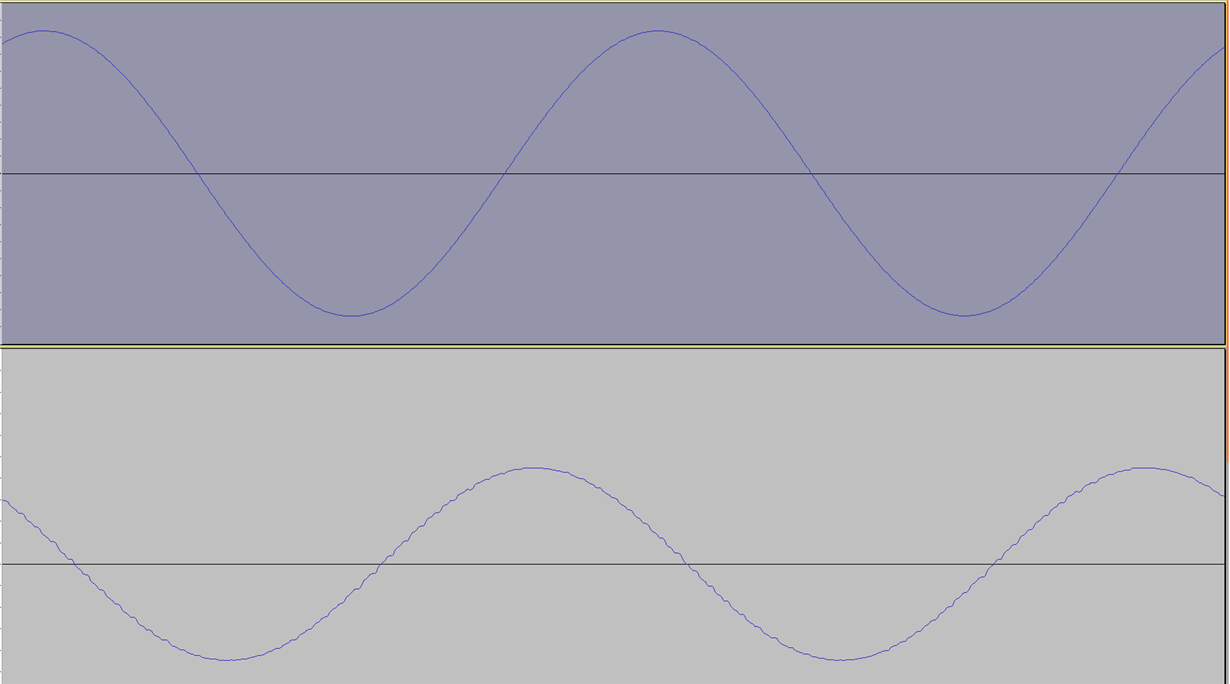

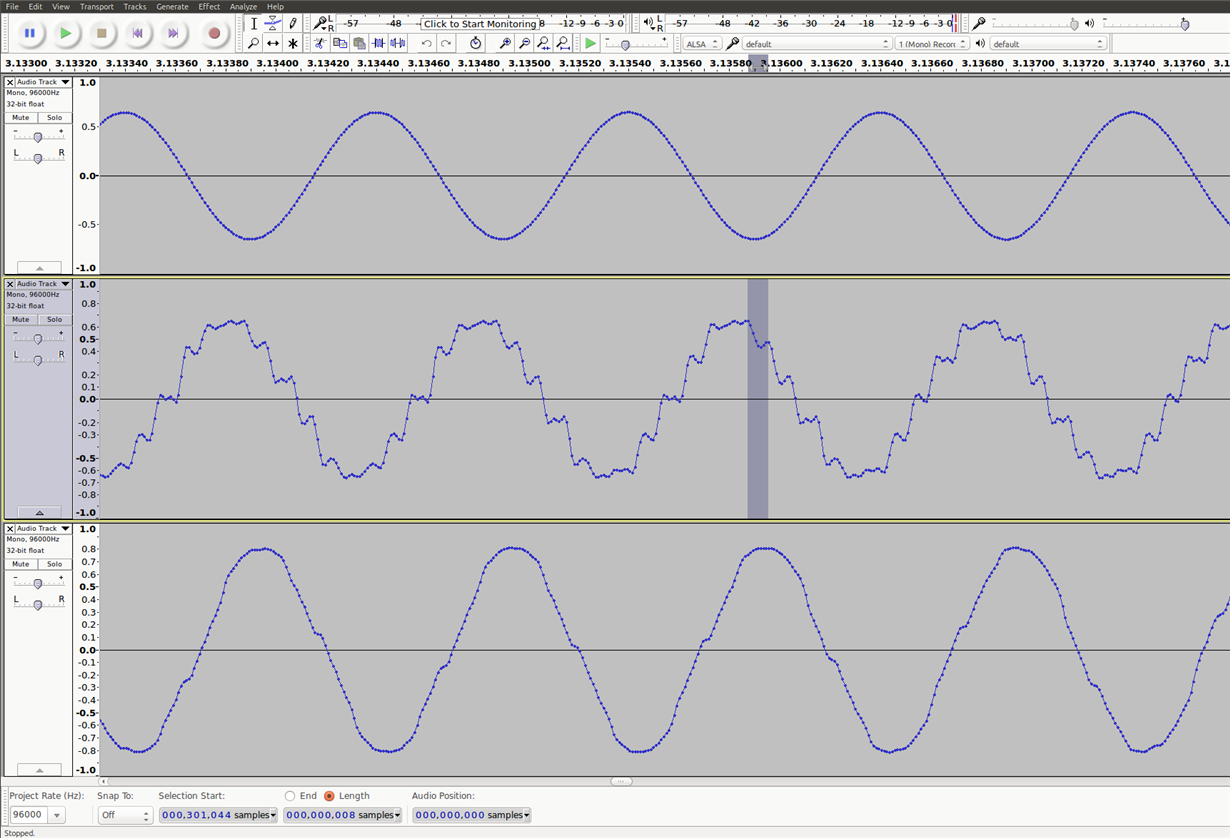

Is there any way I can get some help setting up the sampling rate on the EVMK2G with the TI-RTOS 3.01 PDK? It's stuck at what sounds like a very low sampling rate right now.