Other Parts Discussed in Thread: DP83826EVM

Srinivas (Hope that this gets to you),

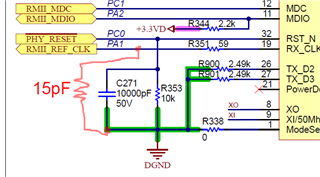

We are moving forward with changing our design to use the DP83826 PHY based on TI's recommendation and our series of testing with the DP83826EVM from our previous thread.

The updated design is attached which replaces the LAN8742A with the DP83826. As discussed previously we are looking forward to your input on the design before we commit to our next build.

Hope that you are doing well - look forward to hearing from you soon.

Take care - Duncan