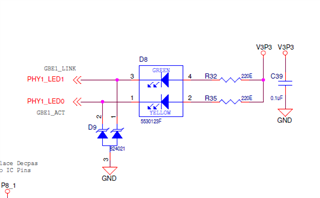

Other Parts Discussed in Thread: DP83869HM, DP83869, TIDA-00928, TIDA-00496, , TIDA-00306

Hi All,

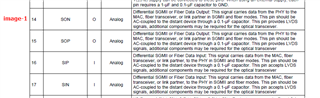

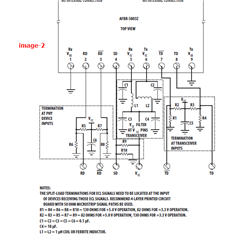

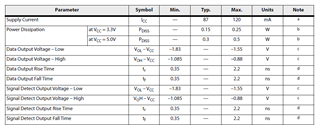

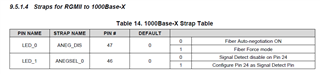

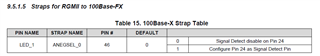

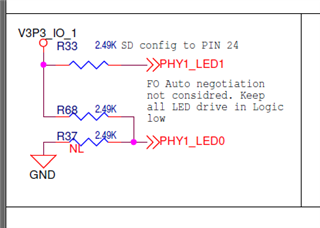

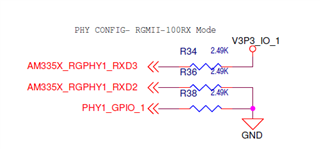

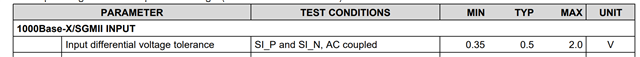

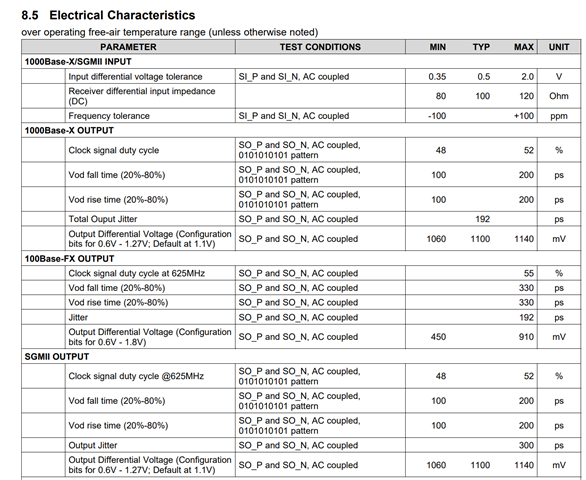

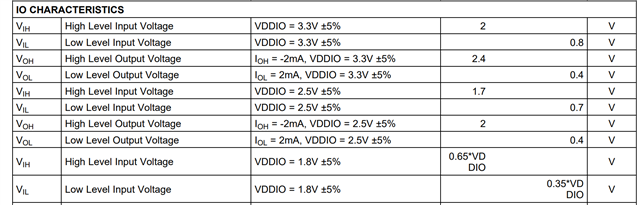

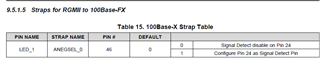

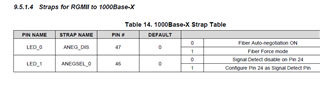

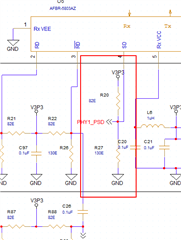

In my project, I need to interface the DP83869HM to the AFBR-5803AZ 100FX fiber module.

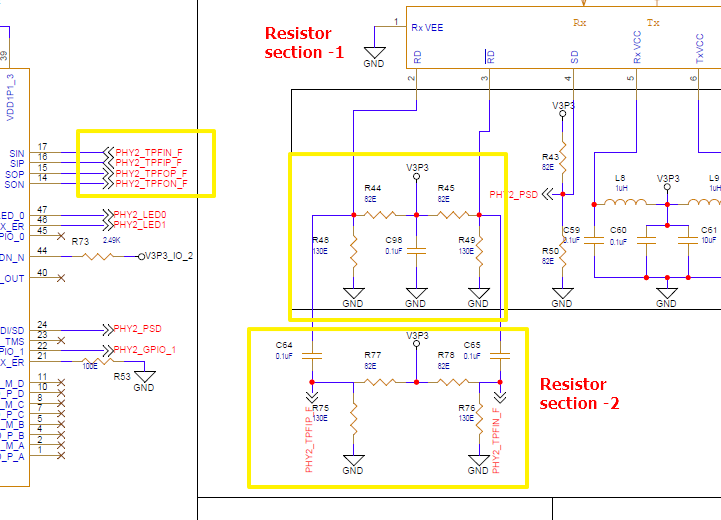

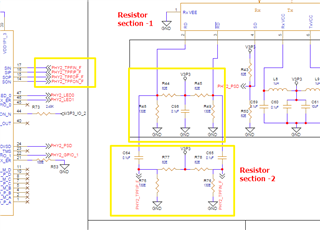

Please refer to the below schematic section and confirm whether required two sets of Resistor divider network in between the Phy to FIber signal.

Also, I have attached a schematic of the PHY and 100FX fiber module section in PDF format.6864.schematic.pdf

Regards

Anees PK.