Part Number: XIO3130

Hi there,

Customer is having an issue with the XIO3130.

Here is the issue:

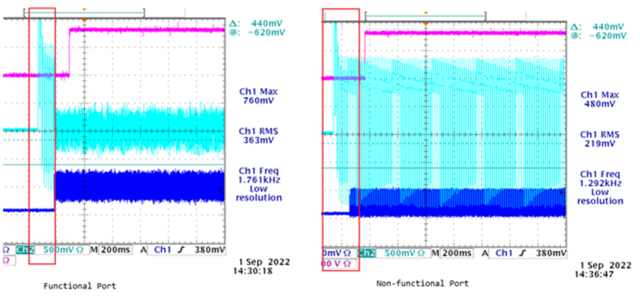

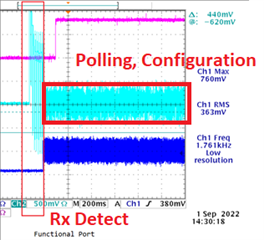

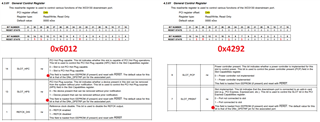

Although the device seems properly strapped, and devices are present on downstream ports 1 and 2, customer is only seeing activity on downstream port 2.

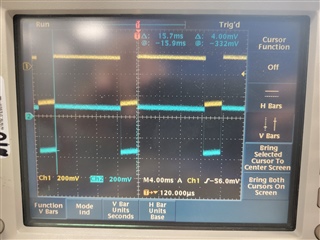

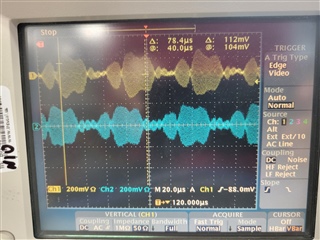

If they scan the PCI bus, they see the device itself, all its downstream ports, as well as the device on downstream port 2, but nothing on downstream port 1 (no reference clock is present – see below)

Even though downstream port 3 is not enabled, there is a reference clock present (100Mhz – see below)

Here is a little more detail:

DN1_DPSTRAP = 3.3V

GPIO[0] = 418 mV (4.7K Resistor)

GPIO[1] = 0V

GPIO[2] = 3.3V

DN1_REFCLKO: No activity

DN2_DPSTRAP = 3.3V

GPIO[4] = 426 mV (4.7K Resistor)

GPIO[5] = 0V

GPIO[6] = 3.3V

DN2_REFCLKO: 100 MHz clock

DN3_DPSTRAP = 0V

GPIO[8] = 3.3V

DN3_REFCLKO: 100 MHz clock

Do you think somebody could help explain this behavior? Anything missed in the datasheet?

Thanks!