Other Parts Discussed in Thread: , DS90UB953-Q1, DS90UB953-Q1EVM, ALP

Hi,

I am working on a project where we are using a deser-ser couple to develop a communication between our board and a remote CSI cmos sensor.

We developed our custom board with the deser (DS90UB954-Q1), following design rules as much as possible.

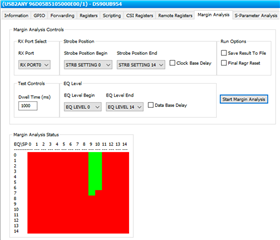

Now, we checked the communication integrity by using the margin analysis, integrated in the Analog LaunchPAD software and we got the following result, which is quite poor:

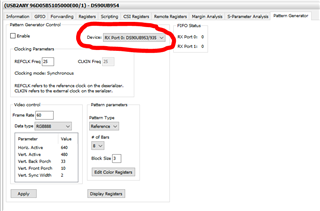

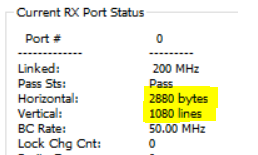

To get the result we used a DS90UB954-Q1EVM evaluation board, we connected the external I2C port to the I2C input of our deser (soldered on our custom board), we checked that our deser had the correct I2C address (different from the address of the deserializer on the EVM board) and we launched the test.

We tried different cable length, but unfortunately the result is similar. Moreover, also using a different port (port 0 or port 1) to connect the coaxial cable the result is the same.

What do you suggest to improve the signal integrity?

Is there another test i can do to better understand what is the problem?

If I send you my PCB design, can you check if there is some macroscopic error?

Thank you in advance.

Best regards,

Alessandro