Other Parts Discussed in Thread: DS90UB933-Q1

Hi team,

My customer is PATEO and the OEM is Dongfeng.

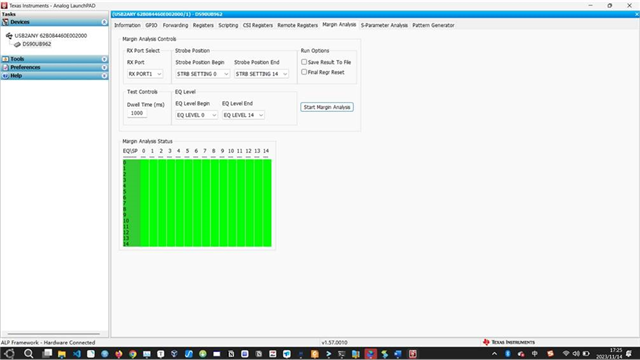

When they only used DS90UB962, they encountered the problem that the surround view camera did not transmit images.

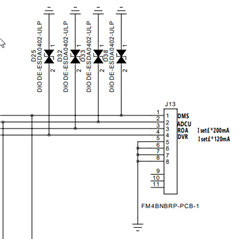

The connection is as follows:

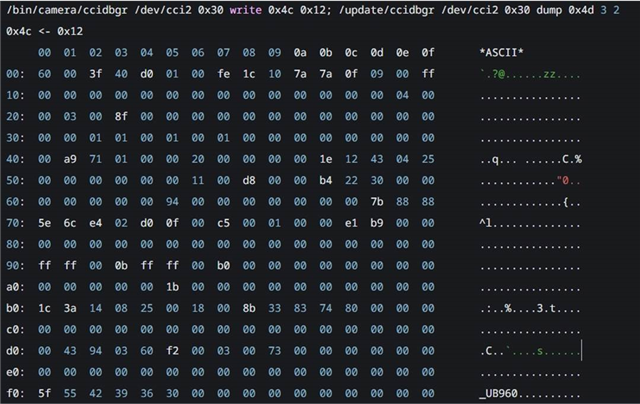

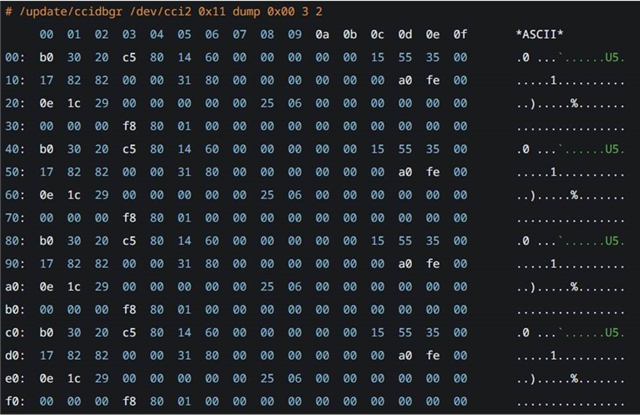

The 962 chip currently used on the 8155 platform is in the mass production stage. It often encounters the problem of being unable to produce pictures. Check the 0x4D/0x4E register and there is indeed an exception. The register value printed in the exception log is as follows:

0xDB = 0x08, 0x4D = 0xc0, 0x4E = 0x0a, 0x7A = 0x02

0xDB = 0x00, 0x4D = 0xc0, 0x4E = 0x02, 0x7A = 0x00

0xDB = 0x08, 0x4D = 0xc1, 0x4E = 0x0c, 0x7A = 0x0f

0xDB = 0x08, 0x4D = 0x40, 0x4E = 0x02, 0x7A = 0x02

0x4D bit0: LOCK_STS: What are the possible reasons for the lock to be lost? We found on site that the lock status may jump repeatedly without plugging or unplugging. What are the possible reasons for this problem?

We think that there are signal integrity issues such as the quality of the wiring harness, connectors and layout, and the jitter of the reference clock input to the front-end serializer. If it is the above reasons, what tests and attempts can customers make to verify the current problem.