Hello, Mellin

I continue my questions in email here.

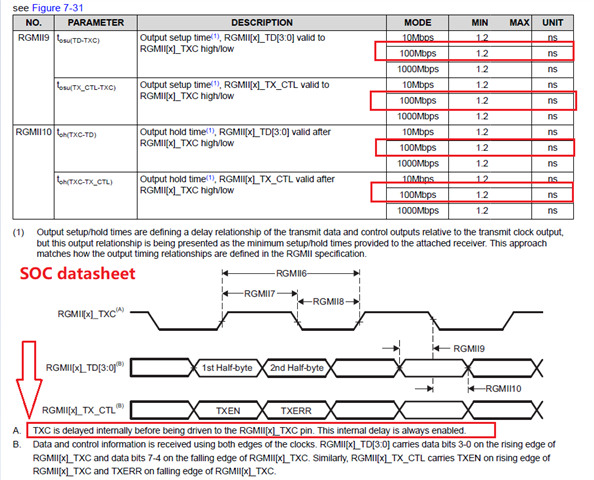

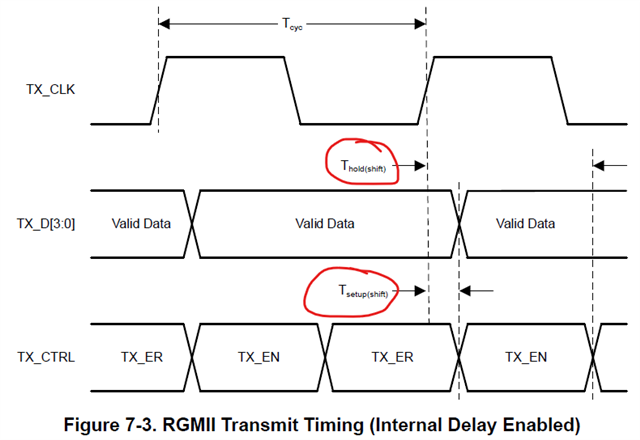

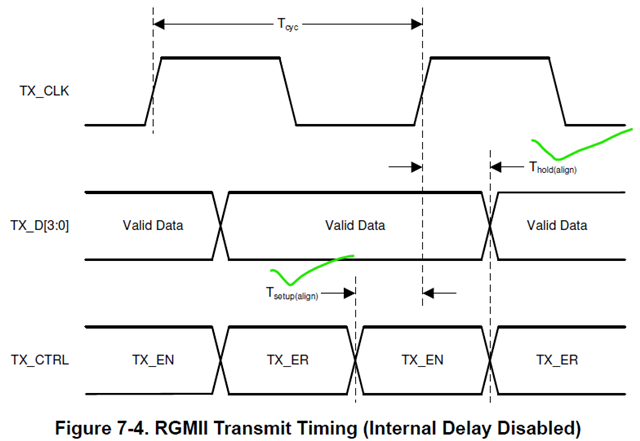

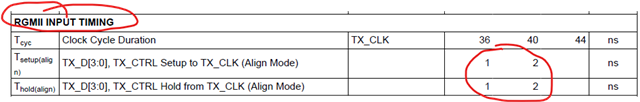

the 100Mbase-T1 RGMII operates in shift mode, communicating with SOC.

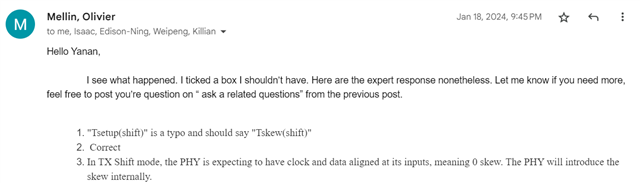

in the email, your reply is as below:

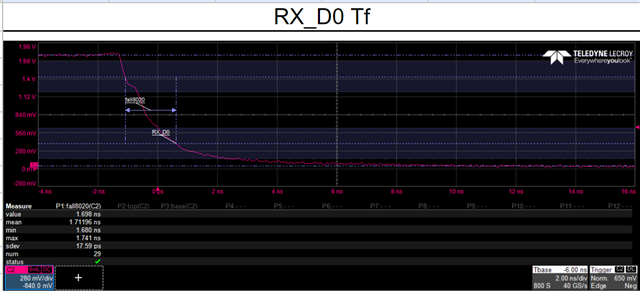

1. about RGMII OUTPUT TIMING:

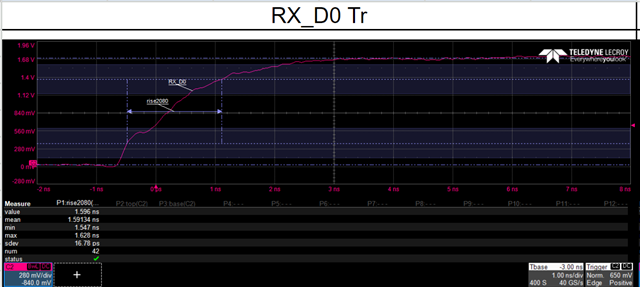

the RX timing parameters are specified at the ouput pin of RGMII RX interface, right?

the parameters need to match the receiver's(SOC) input specification, right?

2. RGMII TX and RX align mode or delayed(shift) mode configuration

in the snapshot reply above, you have confirmed my understanding OK for the configuration below: