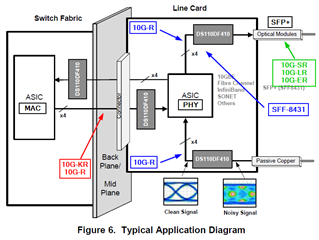

Other Parts Discussed in Thread: DS110DF410

Dear TI Team:

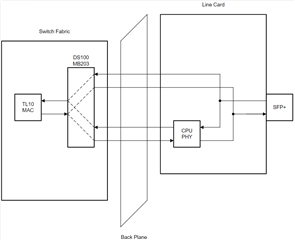

We have DS100MB203 in our design for 10G-KR mux application,

1. Pls review the SCH attached,Thanks

2. In datasheet, There are three functional mode,Pin control mode, SMBUS and external E2PROM,

So the functional mode just can be recognized through Pin_ENSMB when power up, right?

And if I pull RESET to low and then up when normal operation, this functional mode config can be re-recognized or not?

3. If in SMBUS mode, does it mean the level change of pin_SEL0 and pin_SEL1 will be ignored when normal operation, right?

4. If in pin control mode, does it mean the setting of EQ/DE will be fixed by the pull up and down resistor, and will be not changed when normal operation, right?

Best Regards

Lisa