Part Number: TLK10031

Tool/software:

Hi team,

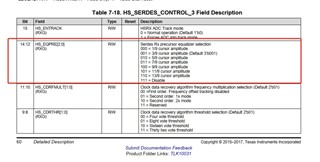

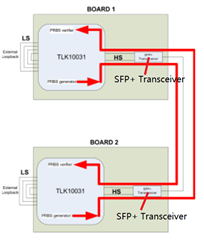

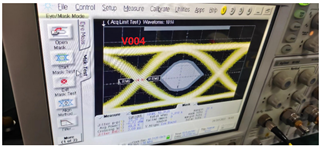

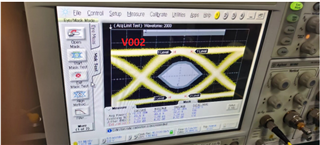

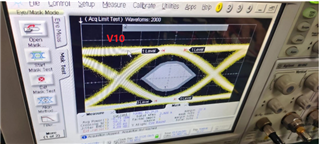

The following screenshot is register bit14:12 traversed, the same value settings does not fit all boards and does not behave consistently, with the best performing optical module, there are still CRC errors for some PHY's Rx. The probability of a board having a problem is about 50 μs, and the replacement of the 10-Gigabit chip will improve.

We want to figure out:

1. How to solve the CRC errors?

2. For a global or RX equalization configuration, which registers can be used to optimize besides HS_SERDES_CONTROL_3?

3. TX on the other side of the RX is pre-emphasis, but it seems no effective on the PHY side.