Part Number: DS90UB934-Q1

I am using the 934 deserializer in conjunction with the 935 serializer connected to a CSI-2 (MIPI) image sensor. The SerDes is in DVP mode with an external FrameSync sourced from the deserializer end.

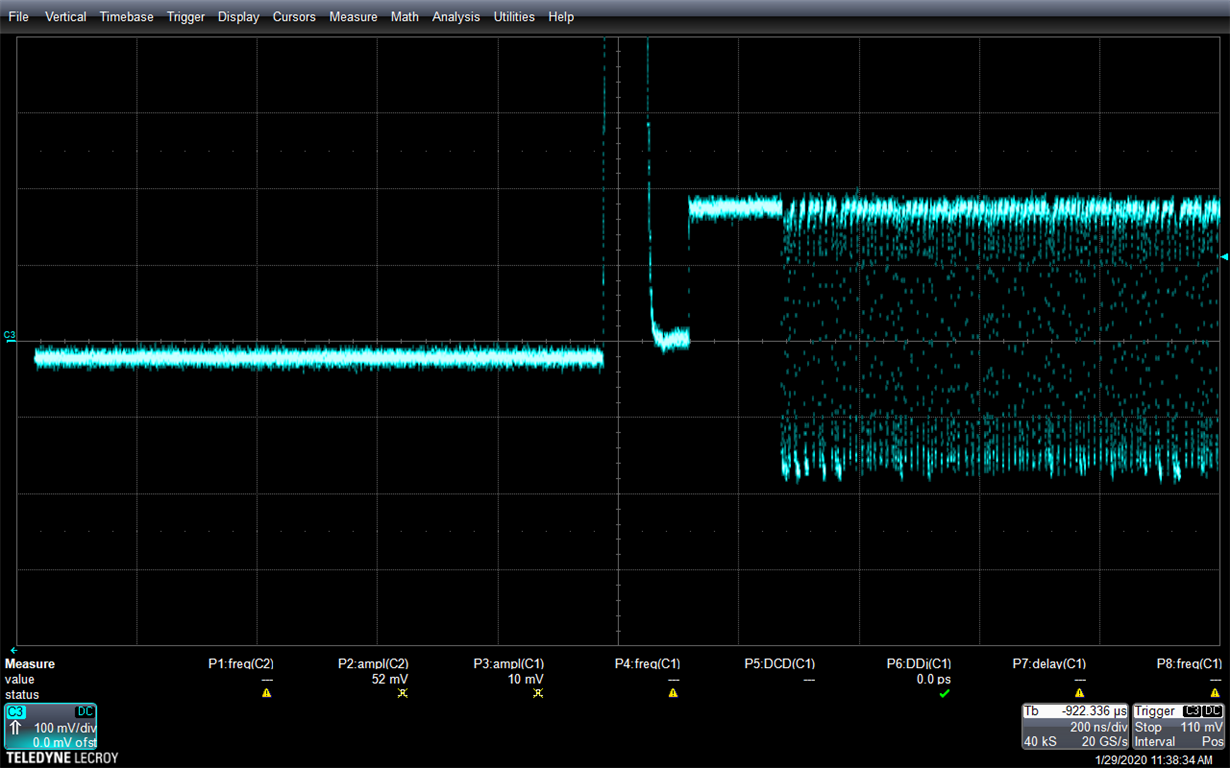

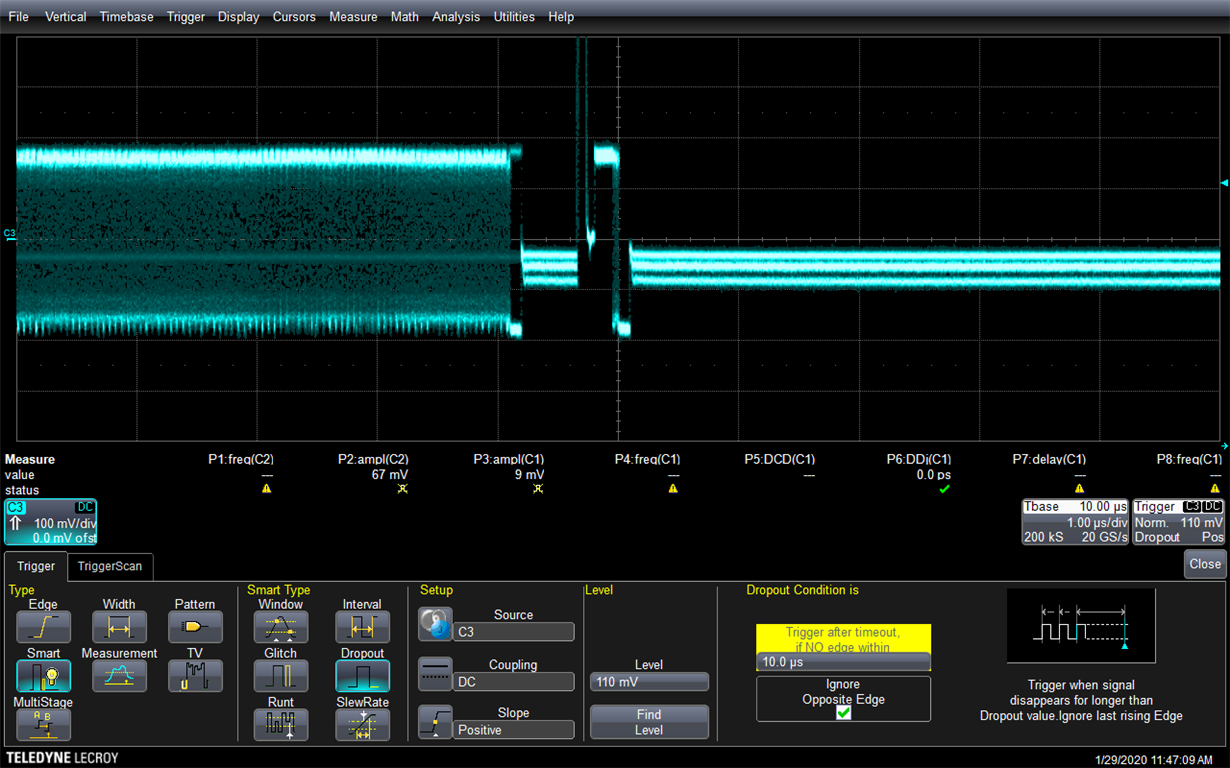

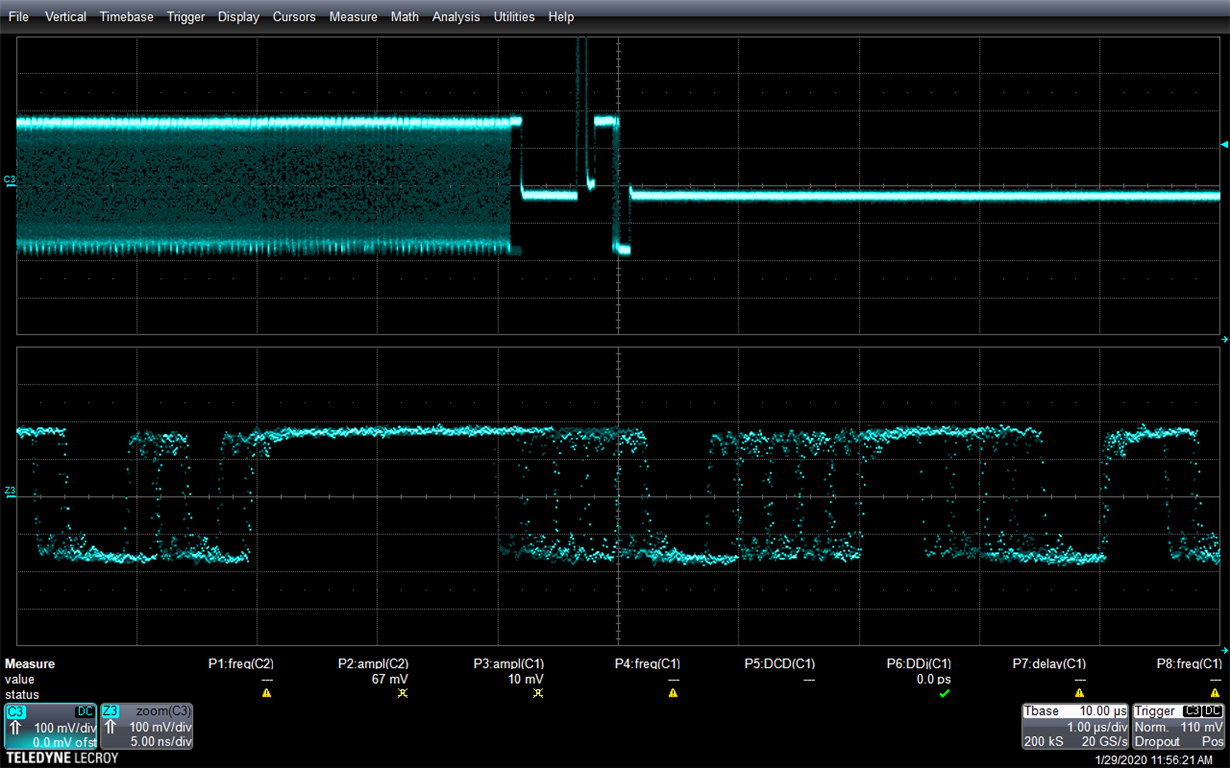

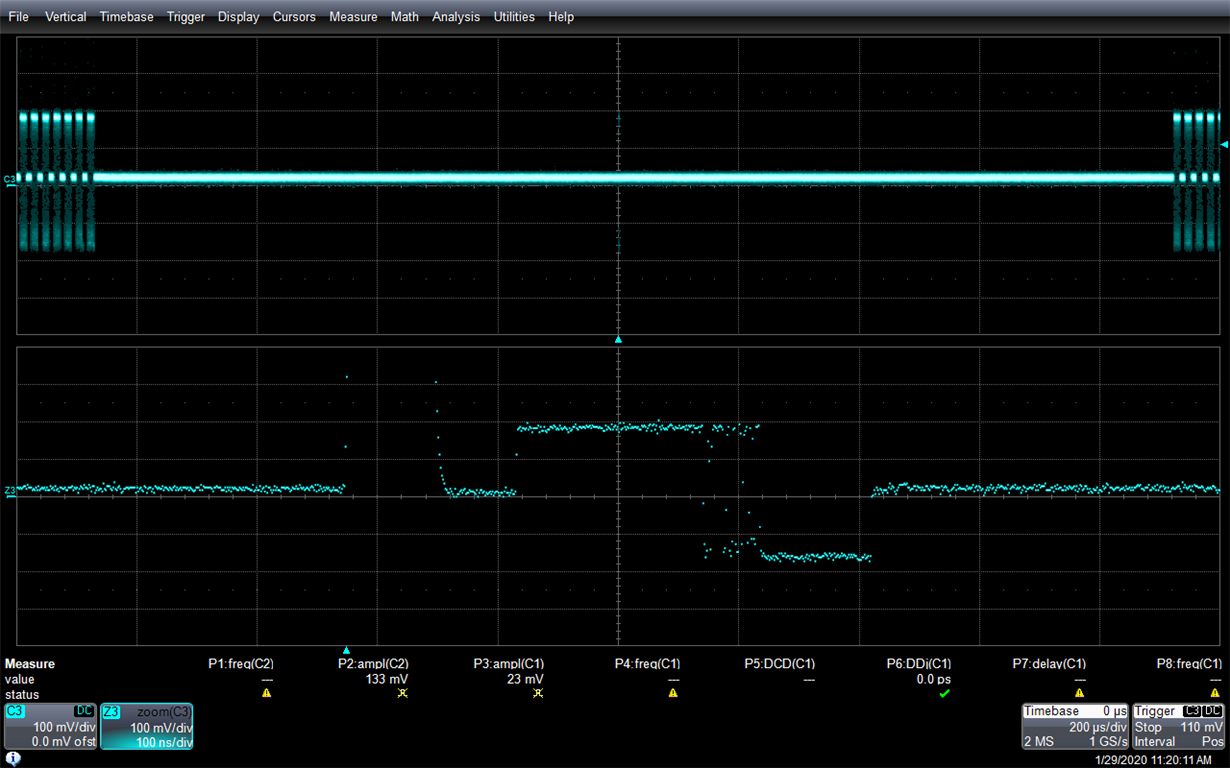

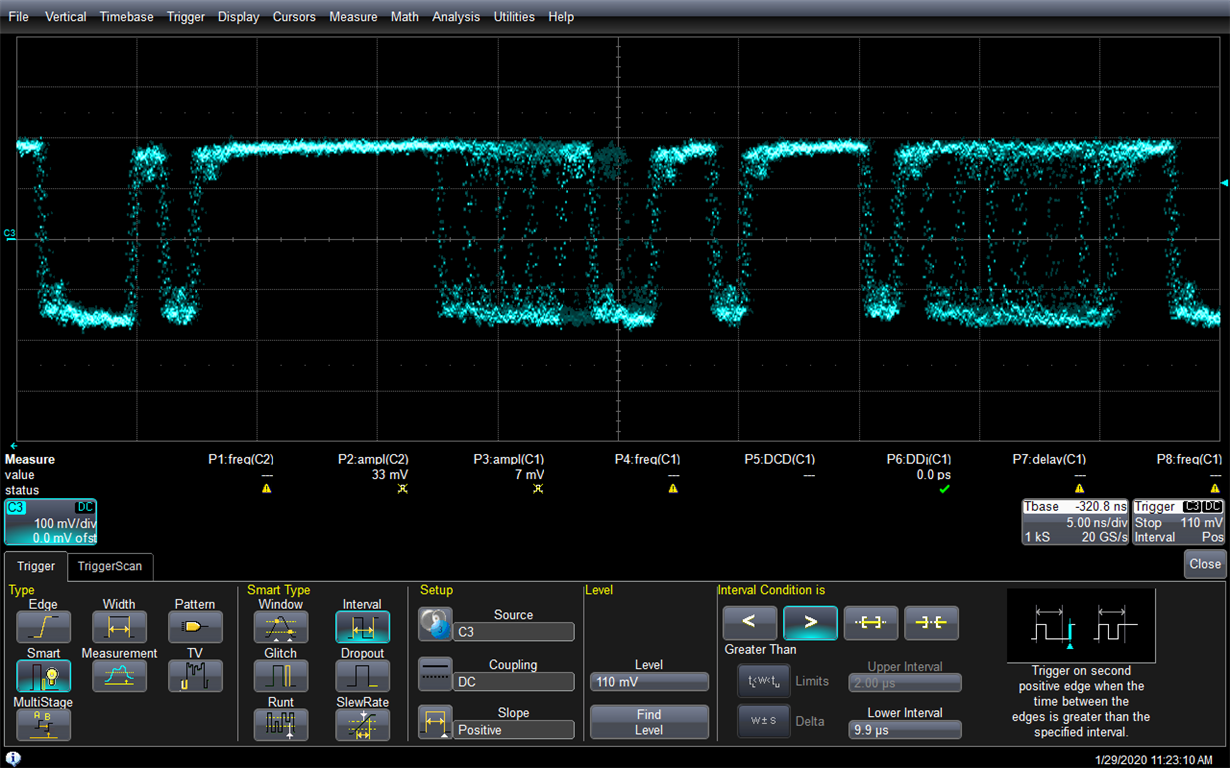

The video data out of the deserializer goes between active and blanking (all zeros) as expected, but HSYNC is always high and VSYNC is always low on their respective deserializer pins.

The issue is similar to this post: https://e2e.ti.com/support/interface/f/138/t/735724

but I am using a CSI serializer so I can't verify SYNC presence in the same way.

I've attached the register settings of the SerDes devices, and noted the ones that have changed between resetting the chips and my initialization functions. Those register settings can be viewed in the table file below. Any other registers not mention can be assumed to be default.

Any advice would be greatly appreciated.

Regards,

Sam Shafer