Other Parts Discussed in Thread: TPS3839, TLV840, SN74LVC1G17

Tool/software:

Hi Team,

This is FAE Jayden, my customer is using SN74LVC1G125, and they have one question about this device.

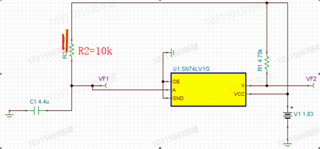

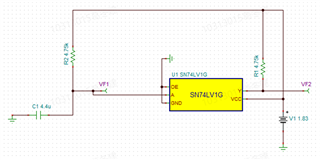

The Schematic is as below:

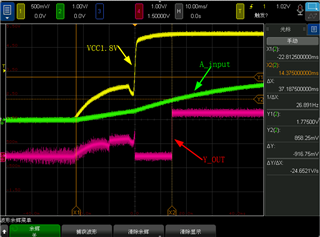

The application conditions are as follows: PinA uses an RC delay circuit, and the PinY output is pulled up to VCC through 4.75kohm.ZTE discovered that when the input of the PinA has not yet reached VIH=0.65*VCC, the Y pin outputs a high level, causing the subsequent devices to reset prematurely. The waveform is as below:

CH1-OUTPUT Y CH2-PINA CH3-ignore Ch4-1.8V VCC

Could you help check the root cause? Many Thanks!

Best regard

Jayden