Hi dear expert,

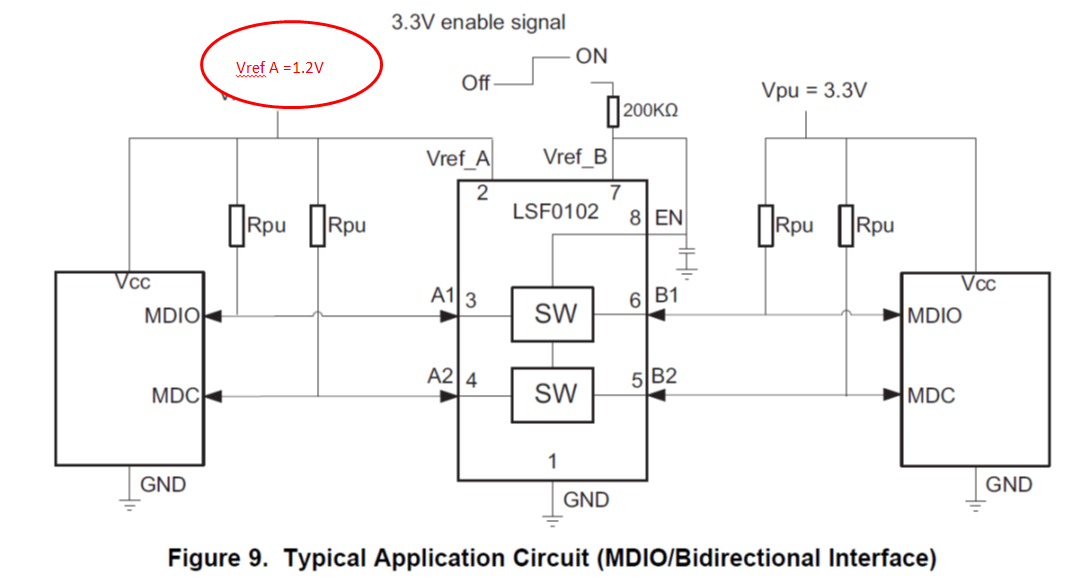

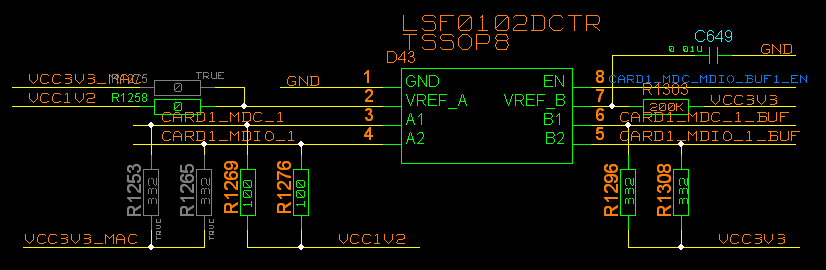

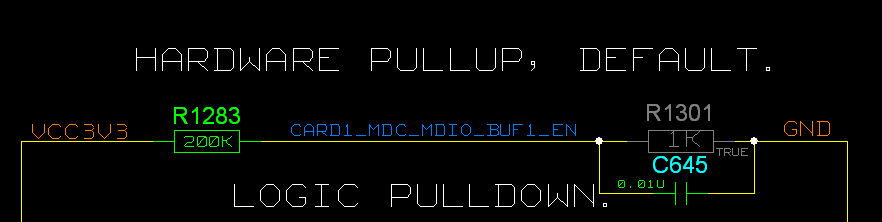

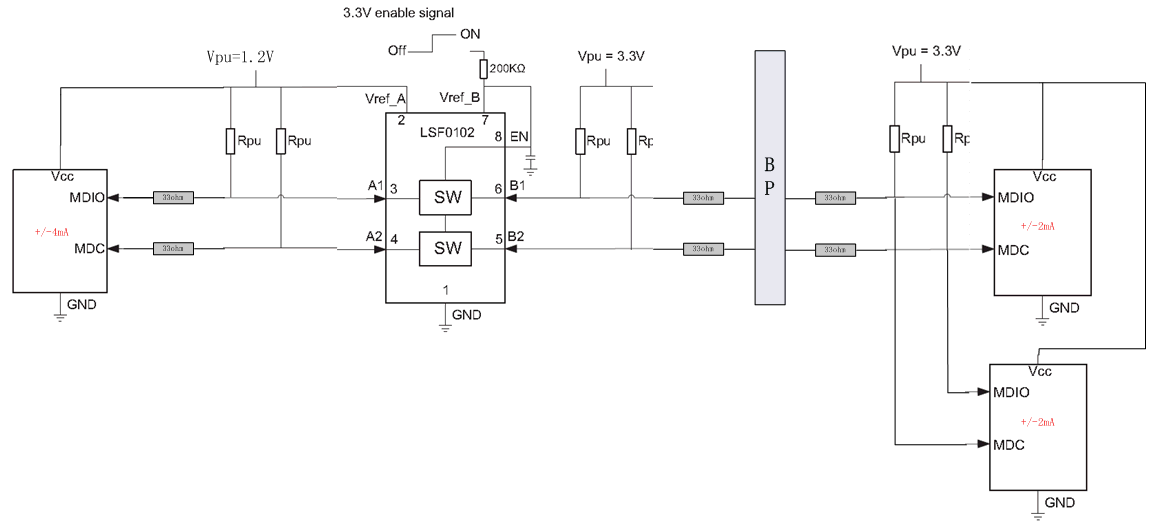

My customer ZTE met some problem when using LSF0102. Their application is 1.2V and 3.3V bidirectional level shifting, the data rate is 25MHz. The schematic is as below:

During test, they found if the data is not sent, the 1.2V and 3.3V level are correct; if data is sent, the 3.3V is only 1.8V.

Have you met this phenomenon? Can you please give us any suggestion or advice.

thanks very much for your support.

BR,

Joyce