Part Number: MCU-PLUS-SDK-AM263X

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

MCU-PLUS-SDK-AM263X: Continuous sampling of multiple ADCs to DMA buffers

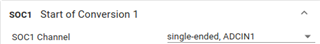

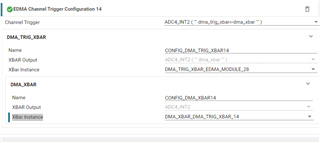

I want to configure multiple ADC channels to continuously read voltage and store the samples to RAM using DMA.

Referring to SDK example: adc_soc_continuous_dma

I have this example working, but the SDK example fills the DMA buffers, and then stops.

I want to modify example such that ADC conversion is continuous for defined number of samples.

I experimented removing the function calls in the ISRs (seen here) which I suspected may be stopping the 'continuous ADC to DMA' that I want.