Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hello TI

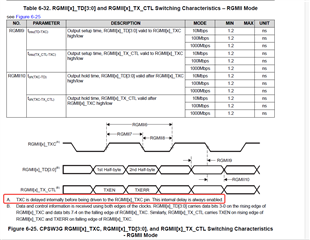

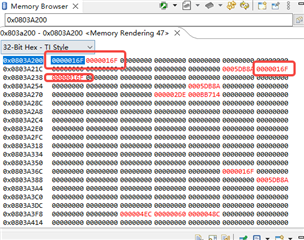

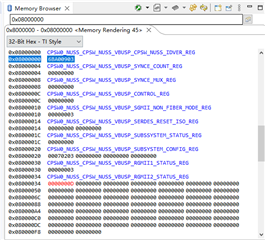

We are testing CPSW ports using LP-AM243, we deleted one ethernet phy which was previous connectted to RGMII1 and replace it with our FPGA,RGMII1 tx channels are not connected to FPGA as we don't send data to FPGA. we want to receive broadcast ethernet frames from FPGA but got nothing.

How can I debug this issue, can you give us some advice,

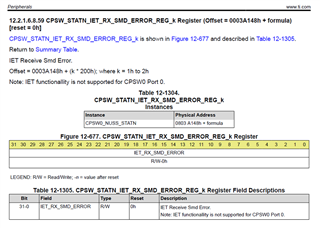

register status is for RGMII1 is 3 which means 100Mbps,

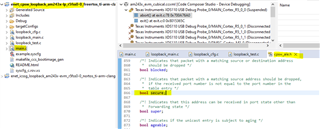

We are using the demo enet_lwip_cpsw in our sdk, and modify the function

This is our test case, please check.

This is our test case, please check.