Part Number: MCU-PLUS-SDK-AM263PX

Other Parts Discussed in Thread: DP83869

Tool/software:

ICSS-EMAC Issue:

I am trying to test the SDK example:

AM263Px MCU+ SDK: ICSS-EMAC Lwip Example (ti.com)

The Control Card is connected to a PC through the on-board RJ-45 (via DP83869).

I understand that PING does not work, but I expect that the ARP request from the PC PINGing the Control Card will trigger an ARP Announcement transmission from the Control Card. However, I see no transmissions from Control Card when running ICSS-EMAC.

I am testing this with Wireshark on the PC.

Test Setup Validation:

When I execute SDK example:.

AM263Px MCU+ SDK: Enet Lwip TCP Client Example (ti.com)

… with the same IP Address, and test setup, I see ARP Announcements being transmitted by the Control Card.

Troubleshooting Steps:

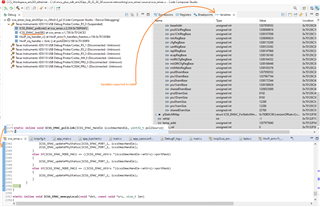

I put breakpoints in icss_emac.c at, ICSS_EMAC_txPacketEnqueue(). This revealed that icss_emac transmit is executing.

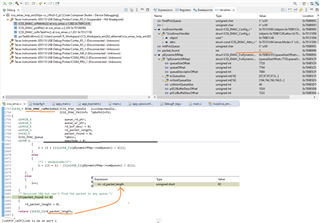

I put a breakpoint in lwip2icss_emac.c at Lwip2Emac_sendTxPackets(). This breakpoint is not hit.

I see this on the console:

|

INFO: Bootloader_socLoadHsmRtFw:82: Device Type : HSFS INFO: Bootloader_socLoadHsmRtFw:84: HSMRT Size in Bytes : 24739 INFO: Bootloader_socLoadHsmRtFw:97: hsm runtime firmware load complete ... Starting NULL Bootloader ... INFO: Bootloader_runCpu:155: CPU r5f1-1 is initialized to 400000000 Hz !!! INFO: Bootloader_runCpu:155: CPU r5f1-0 is initialized to 400000000 Hz !!! INFO: Bootloader_runCpu:155: CPU r5f0-1 is initialized to 400000000 Hz !!! [BOOTLOADER_PROFILE] Boot Media : undefined KPI_DATA: [BOOTLOADER_PROFILE] Boot Image Size : 0 KB [BOOTLOADER_PROFILE] Cores present : KPI_DATA: [BOOTLOADER PROFILE] System_init : 941us KPI_DATA: [BOOTLOADER PROFILE] Drivers_open : 142us KPI_DATA: [BOOTLOADER PROFILE] LoadHsmRtFw : 29804us KPI_DATA: [BOOTLOADER_PROFILE] SBL Total Time Taken : 58653us

NULL Bootloader Execution Complete... INFO: Bootloader_loadSelfCpu:207: CPU r5f0-0 is initialized to 400000000 Hz !!! INFO: Bootloader_runSelfCpu:217: All done, reseting self ... MII mode load to PRU0 passed load to PRU1 passed Starting lwIP, local interface IP is 192.168.2.252 [LWIPIF_LWIP]Link is Up on port 1 [LWIPIF_LWIP] Interface layer handle is Initialised [LWIPIF_LWIP] NETIF INIT SUCCESS status_callback==UP, local interface IP is 192.168.2.252 UDP server listening on port 5001 link_callback==UP 6. 26s : CPU load = 0.96 % 11. 26s : CPU load = 0.73 % 16. 26s : CPU load = 0.74 % 21. 26s : CPU load = 0.72 % 26. 26s : CPU load = 0.75 % 31. 26s : CPU load = 0.75 % 36. 26s : CPU load = 0.74 % 41. 26s : CPU load = 0.74 % 46. 26s : CPU load = 0.79 % [LWIPIF_LWIP]ERROR: Rx Pbuf_alloc() in LWIPIF_LWIP_INPUT failure.!

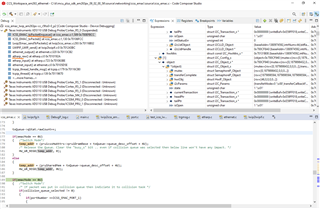

[LWIPIF_LWIP]ERROR: Rx Pbuf_alloc() in LWIPIF_LWIP_INPUT failure.! [LWIPIF_LWIP]ERROR: Rx Pbuf_alloc() in LWIPIF_LWIP_INPUT failure.! [LWIPIF_LWIP]ERROR: Rx Pbuf_alloc() in LWIPIF_LWIP_INPUT failure.! [LWIPIF_LWIP]ERROR: Rx Pbuf_alloc() in LWIPIF_LWIP_INPUT failure.! [LWIPIF_LWIP]ERROR: Rx Pbuf_alloc() in LWIPIF_LWIP_INPUT failure.! [LWIPIF_LWIP]ERROR: Rx Pbuf_alloc() in LWIPIF_LWIP_INPUT failure.! [LWIPIF_LWIP]ERROR: Rx Pbuf_alloc() in LWIPIF_LWIP_INPUT failure.! [LWIPIF_LWIP]ERROR: Rx Pbuf_alloc() in LWIPIF_LWIP_INPUT failure.! [LWIPIF_LWIP]ERROR: Rx Pbuf_alloc() in LWIPIF_LWIP_INPUT failure.! [LWIPIF_LWIP]ERROR: Rx Pbuf_alloc() in LWIPIF_LWIP_INPUT failure.! [LWIPIF_LWIP]ERROR: Rx Pbuf_alloc() in LWIPIF_LWIP_INPUT failure.! [LWIPIF_LWIP]ERROR: Rx Pbuf_alloc() in LWIPIF_LWIP_INPUT failure.! [LWIPIF_LWIP]ERROR: Rx Pbuf_alloc() in LWIPIF_LWIP_INPUT failure.! pbuf_free: p->ref > 0ASSERT: 46.796612s: /nightlybuilds/mcupsdk_internal/jenkins/mcu_plus_sdk_am263px_09_02_00_56/source/networking/lwip/lwip-stack/src/core/pbuf.c:pbuf_free:755: 0 failed !!!

I also see this on the console: …

[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilaisation[LWIPIF_LWIP]Packet Dropped!: Rx callback is called before Interface layer handle initilais

I only notice the above error on the console when I halt the processor at a breakpoint. It Is possible that this causes a race condition.

Here are some expressions I captured when halted at ICSS_EMAC_txPacketEnqueue():

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||