Other Parts Discussed in Thread: SYSCONFIG, , TMDSHSECDOCK-AM263

Tool/software:

Hi

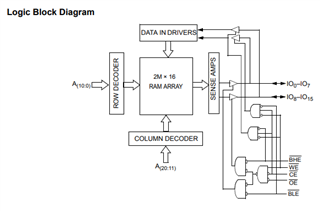

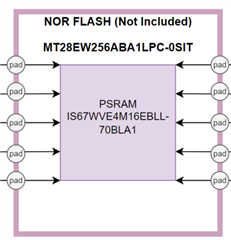

Based on the " TMDSHSECDOCK-AM263", it is shown the compatible flash/SRAM devices include 256 Mb device.

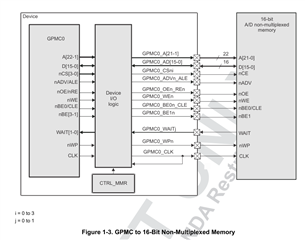

But as per SysConfig tool the address bits available from A0 to A21 (22 bits). To support 256 Mb SRAM, 23 bits are required.

Suggest to which pin of GPMC, the 23th address bit to be connected ?

Can it be connected to CS pin ?

Is AM2634 device drivers available only for SRAM or Flash of size less than 256Mb only ?

Regards

Bivin