Other Parts Discussed in Thread: INA282, TM4C1294NCPDT, LM3S8971

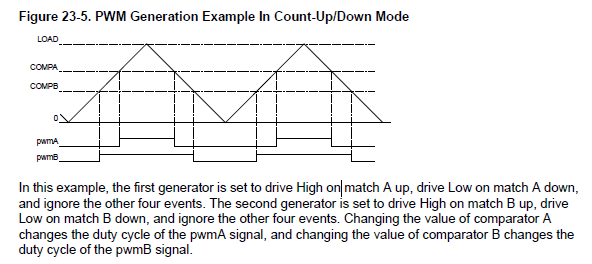

Figure 23-5 below infers there to be only a single pulse on A or B PWM output Up/Down counter mode during load and zero count match. An attempt was made in an earlier illustration of the up/down PWM generator counter to show a reoccurring pulse stream in a very confusing way. A single output pulse from PWM generator A&B is then shown to occur for the zero to zero transition below.

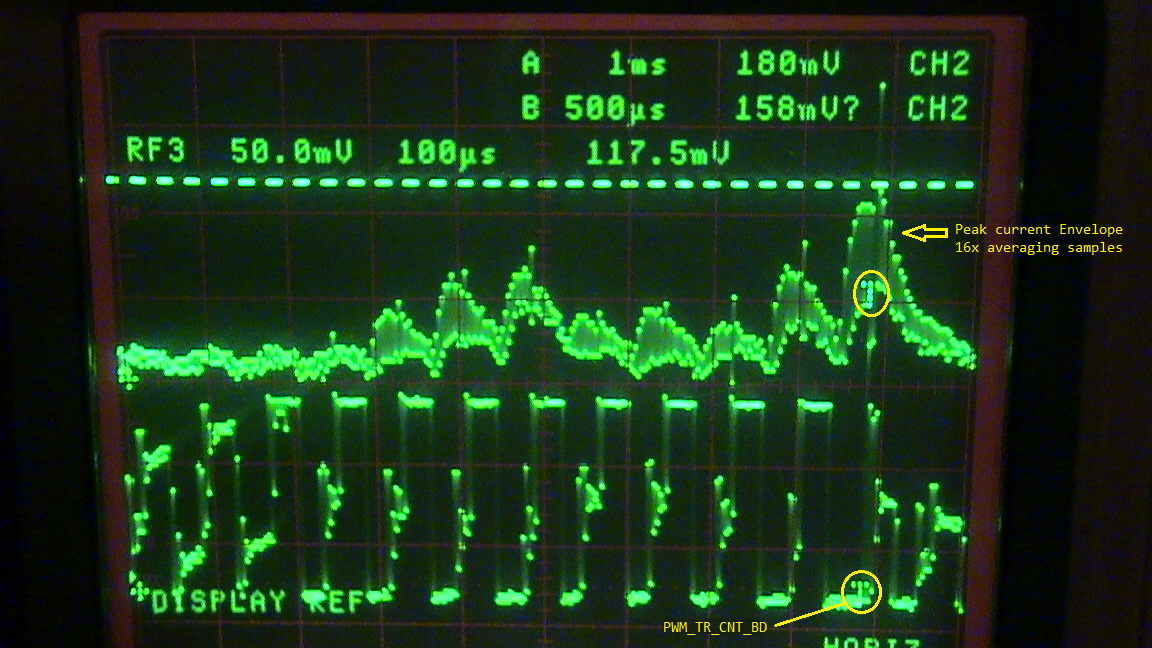

Might the PWM generator A&B output signal be drawn incorrectly in relation to the discussion on the PWM up/down counter mode? Does the PWM generator output only a single pulse for a incremental up/down count of many integers only when the comparators match a set point in the sloping integer count? If so in a 20Khz PWM frequency & resulting trapezoidal wave form a single PWM generator period of integer counts results in a single 50us pulse inside the trapezoidal wave form over 1ms in horizontal length. More over then load count match occurs at the peak of every 50us pulse with (zero) count pulse on either side of each and every 50us generator pulse. Possibly this topic has been over simplified to the point it makes no sense in relation to the Tivaware C++ programming of the PWM generators and other functions. Tivaware is not alone Stellarisware departing with the same diverged datasheet topic to actual occurring PWM events in the real world of DSP leaves one scratching head, beard and or whiskers!

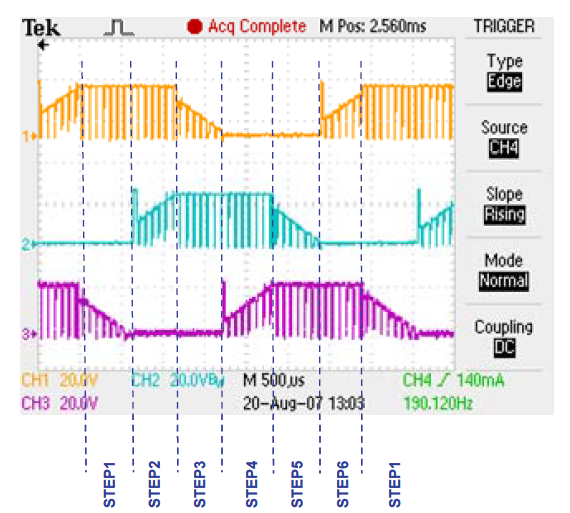

This figure below does not make that point clear as it relates to the resulting trapezoidal wave form or center aligned PWM pulse stream when (pwmA & pwmB) are not shown to have more than one rising and one falling edge. The relation to this diagram and the resulting trapezoidal wave forms (below) figure 23-5 share similar pyramid architectures making a through understating of it even more confusing.